1. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the DSI peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

The DSI peripheral implements all the protocol functions defined in the MIPI® Display Serial Interface (MIPI® DSI) specification. It provides an interface to communicate with a DSI-compliant display. The MIPI® DSI is part of a group of communication protocols defined by the MIPI® Alliance [1].

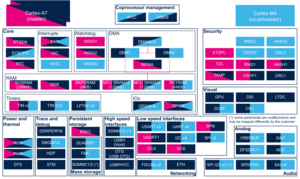

On STM32MP15x lines ![]() , the DSI peripheral supports:

, the DSI peripheral supports:

- up to 2 D-PHY data lanes.

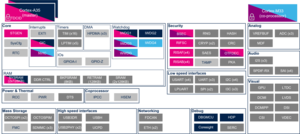

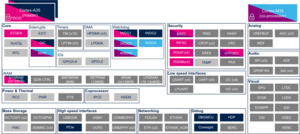

On STM32MP23x lines ![]() and STM32MP25x lines

and STM32MP25x lines ![]() , the DSI peripheral supports:

, the DSI peripheral supports:

- up to 4 D-PHY data lanes.

- the RIF security architecture: The RISUP differentiates the access right of accesses performed toward the following RIF protected peripheral ID:

- "DSI_CMN": DSI common registers for DSI-wrapper and DSI-Host

- "DSI_TRIG": DSI Wrapper trigger-A to update a smart panel

- "DSI_RD": DSI-Host read access to a smart panel

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the FwST-M Package running on the Arm® Cortex®-M processor.

Even if some MIPI DSI modes are supported by the DSI internal peripheral, in practice:

- software frameworks like U-Boot or Linux® kernel do not support all the possible modes.

- hardware integration constraints such as support for all the clock values or the pll configurations make it difficult to use all possible modes.

Select a MIPI DSI panel or bridge supporting the DSI video burst mode [2] because this mode is supported by all software frameworks and is easier to fine tune. Please consider the following recommendations when selecting a MIPI DSI panel or bridge for your project:

- Pixel data transmission

- in DSI command mode: not supported by neither U-Boot nor Linux® kernel, use instead the DSI video burst mode.

- in DSI video mode:

- burst mode: supported

- non-burst mode with sync events or pulses: supported with clock constraints to be considered [2].

- Command transmission (initialization sequence, backlight...)

If non-burst mode has to be used for a specific MIPI DSI panel or bridge, check non-burst mode constraints.

3.1. Boot time assignment[edit | edit source]

The DSI is used at boot time for displaying a splash screen through the U-Boot framework.

3.1.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 nonsecure (U-Boot) | |||

| Visual | DSI | DSI | ☐ | |||

3.1.2. On STM32MP23x lines  and STM32MP25x lines

and STM32MP25x lines  [edit | edit source]

[edit | edit source]

3.1.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Visual | DSI |

DSI | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | |||

The below table shows the possible boot time allocations for the features of the DSI instance.

| Feature | Boot time allocation |

Comment | ||

|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | ||

| DSI_CMN | ☐ | |||

| DSI_RD | ☐ | |||

| DSI_TRIG | ☐ | |||

3.1.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Visual | DSI |

DSI | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | ||||

The below table shows the possible boot time allocations for the features of the DSI instance.

| Feature | Boot time allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | ||

| DSI_CMN | ☐ | ||||

| DSI_RD | ☐ | ||||

| DSI_TRIG | ☐ | ||||

3.2. Runtime assignment[edit | edit source]

3.2.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Visual | DSI | DSI | ☐ | |||

3.2.2. On STM32MP23x lines  [edit | edit source]

[edit | edit source]

The table below is applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP23 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Visual | DSI |

DSI | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | ||||

The below table shows the possible runtime allocations for the features of the DSI instance.

| Feature | Runtime allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | ||

| DSI_CMN | ⬚OP-TEE | ☐ | ⬚ | ☐ | |

| DSI_RD | ⬚OP-TEE | ☐ | ⬚ | ☐ | |

| DSI_TRIG | ⬚OP-TEE | ☐ | ⬚ | ☐ | |

3.2.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The table below is applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP25 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Visual | DSI |

DSI | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | |||||

The below table shows the possible runtime allocations for the features of the DSI instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| DSI_CMN | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||

| DSI_RD | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||

| DSI_TRIG | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||

4. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the DSI peripheral for the embedded software components listed in the above tables.

- Linux®:

- DRM/KMS framework

- Linux kernel: drivers/gpu/drm/stm/dw_mipi_dsi-stm.c (the main stm dsi driver with dsi phy)

- Linux kernel: drivers/gpu/drm/bridge/synopsys/dw-mipi-dsi.c (dw dsi bridge driver used by the main stm dsi driver)

- U-Boot:

- U-Boot framework (for the display splash screen)

- drivers/video/stm32/stm32_dsi.c (the main stm32 dsi driver with dsi phy)

- drivers/video/dw_mipi_dsi.c (dw dsi bridge driver used by the main stm32 dsi driver)

- STM32Cube:

5. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

See also additional information in the DSI device tree configuration article for Linux®.

6. How to go further[edit | edit source]

You may be interested in the following related articles:

Refer to the STM32 DSI application note (AN4860) [2] for a detailed description of the DSI peripheral and applicable use-cases.

Even if this application note is related to STM32 microcontrollers, it also applies to STM32 MPUs.

6.1. Non-burst mode constraints[edit | edit source]

In MIPI® DSI video burst mode, the setting for the DSI peripheral's PLL is quite relaxed. The DSI peripheral can send out pixel data in bursts, at rate higher that the pixel clock frequency. The consumer of the pixel data (the MIPI DSI display panel or bridge) will internally re-sample such data to the correct clock frequency. This makes easy to configure the DSI in video burst mode.

In MIPI® DSI video non-burst mode, instead, the DSI peripheral must send out the pixel data at the exact pixel clock frequency required by the MIPI DSI display panel or bridge. But, the set of pixel clock frequencies allowed by the DSI peripheral is limited by:

- the input frequency of the DSI peripheral's PLL (linked to the HSE oscillator on STM32MP15x lines

or to a flexgen clock on STM32MP23x lines

or to a flexgen clock on STM32MP23x lines  and STM32MP25x lines

and STM32MP25x lines  );

); - the programmability of the DSI peripheral's PLL;

- the min and max frequency of the VCO of the DSI peripheral's PLL;

- the selected bit per pixel.

6.1.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

The following script dumps all the possible pixel clock frequencies allowed, that can be checked against the pixel clock frequency required by the MIPI DSI panel or bridge.

#!/bin/bash

hse=24000000

vcomin=1000000000

vcomax=2000000000

n_lanes=2

# 24 bpp

byte_per_pixel=3

for i in {1..7}; do

for n in {10..125}; do

vco=$(($hse*2*$n/$i))

if [ $vco -lt $vcomin -o $vco -gt $vcomax ]; then

continue

fi

for o in 1 2 4 8; do

hs_clk=$(($hse*$n/($i*$o)))

echo $(($hs_clk*$n_lanes/(8*$byte_per_pixel)))

done

done

done | sort -nu

If the required frequency is not listed, you can either:

- check the spec or contact the vendor of the MIPI DSI panel or bridge to identify other pixel clock frequencies allowed;

- consider using a different frequency for the HSE oscillator.

It is possible to change the value of the variables in the script to dump the pixel clock frequencies for different HSE oscillators. Please also check in ROM code overview the values of HSE oscillator's frequency accepted by the BootROM. By changing the HSE oscillator, the Clock device tree configuration in TF-A and OP-Tee device tree must be aligned too.

6.1.2. On STM32MP23x lines  and STM32MP25x lines

and STM32MP25x lines  [edit | edit source]

[edit | edit source]

The DSI internal peripheral and related clock programmability on STM32MP23x lines ![]() and STM32MP25x lines

and STM32MP25x lines ![]() is good enough for supporting the MIPI® DSI video non-burst mode without modifying the HSE reference clock frequency.

is good enough for supporting the MIPI® DSI video non-burst mode without modifying the HSE reference clock frequency.

7. References[edit | edit source]