This article gives information about the support power management in OpenSTlinux for STM32MP1 series.

1. Framework purpose[edit | edit source]

The purpose of this article is to explain how OpenSTlinux components handle the STM32MP1 series power management:

- Software overview

- Peripheral power support

- Low-power modes available on the device

See also the page How to define your low-power strategy.

2. Software overview[edit | edit source]

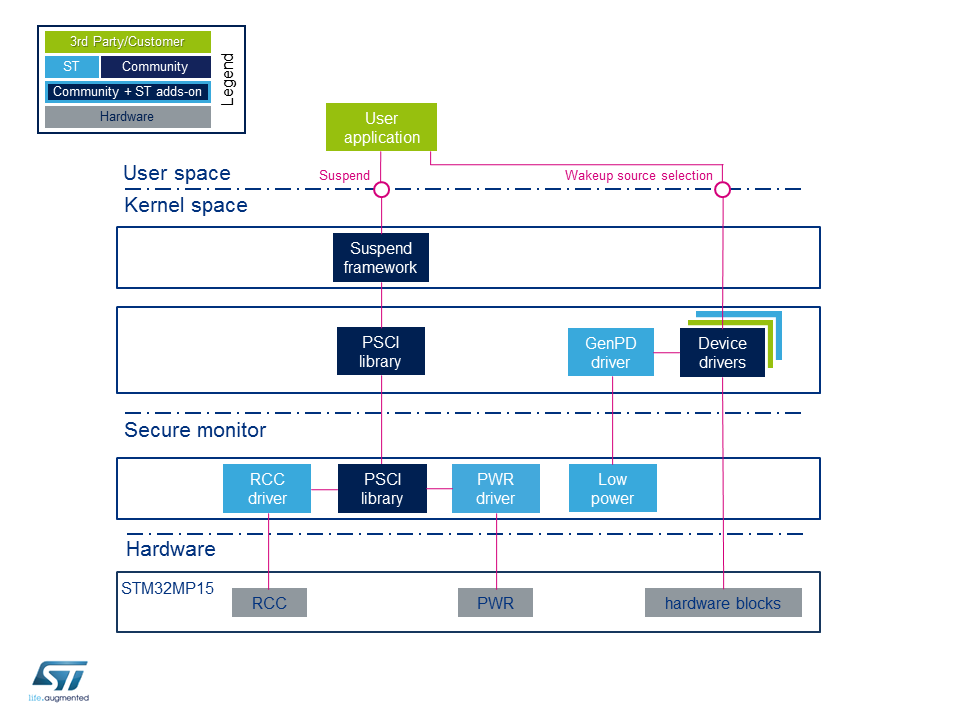

The system power request is handled with the PSCI support and OP-TEE.

The power requests associated to each device (clock, regulator, operation point) are consolidated by the Linux frameworks, and can be handled by a Linux driver or by OP-TEE through SCMI requests.

2.1. Component description[edit | edit source]

The OpenSTLinux components for low-power modes are:

Nonsecure world (Linux):

- Power management frameworks: See Power overview for details

- PSCI library: this is a set of standardized functions to request a low-power service to the secure monitor.

- SCMI drivers: driver for system resources (clock, regulators, power domain,...), exposed by OP-TEE with SCMI protocol.

- Device driver: any peripheral driver which needs to control power.

- RCC driver for clock and reset managed by nonsecure world.

Secure monitor and secure world components (OP-TEE):

- Low-power driver: the role of this driver is to choose the low-power mode according to the programmed wake-up source(s).

- PWR driver: this driver is responsible for configuring the low-power mode.

- RCC driver: this driver handles the circuit secure clocks.

- PSCI libray: generic PSCI stack.

STM32 peripherals (hardware):

2.2. API description[edit | edit source]

The OpenSTLinux power management support is based on Arm® interface specifications:

- Power state coordination interface (PSCI) [1] defines many messages (see identifiers in TF-A include/lib/psci/psci.h or in Linux include/kvm/arm_psci.h ), for examples:

- CPU_ON/CPU_OFF : used for hotplug feature.

- SYSTEM_OFF : used for power off.

- SYSTEM_RESET : used for system reset.

- SYSTEM_SUSPEND : used to system suspend (deep).

- PSCI_VERSION : return the supported version of the PSCI specication, v1.1 is supported by TF-A.

- System Control and Management Interface (SCMI)[2], see SCMI overview for details.

3. Configuration[edit | edit source]

The objective of this chapter is to explain how to configure OpenSTLinux for low-power modes.

See the page power overview for kernel configuration details.

3.1. Supported power modes in OP-TEE[edit | edit source]

The default system low-power mode mapping can be modified through the secure monitor device tree, as described in OP-TEE documentation/devicetree/bindings/regulator/st,stm32mp1-pwr-reg.yaml .

Find below an example in OP-TEE core/arch/arm/dts/stm32mp135f-dk.dts

&pwr_regulators {

system_suspend_supported_soc_modes = <

STM32_PM_CSLEEP_RUN

STM32_PM_CSTOP_ALLOW_LP_STOP

STM32_PM_CSTOP_ALLOW_LPLV_STOP

STM32_PM_CSTOP_ALLOW_LPLV_STOP2

STM32_PM_CSTOP_ALLOW_STANDBY_DDR_SR

>;

system_off_soc_mode = <STM32_PM_SHUTDOWN>;

};

3.2. STPMIC configuration for low-power mode in OP-TEE[edit | edit source]

Refer to PMIC OP-TEE page for details of PMIC configuration in OP-TEE for each power mode, and to application note AN5260 and AN5587 for configuration examples.

In OpenSTLinux, the selected PSCI power level is indicated to OP-TEE with Secure-EL1 Payload Dispatcher (SPD) PSCI hooks. The power level is then consolidated with the genPD power domains state and indicated with pm_hint to each OP-TEE drivers to save/restore the device configuration (see core/include/kernel/pm.h and core/arch/arm/plat-stm32mp1/stm32mp_pm.h for details).

This hook is used by the STPMIC1 driver in OP-TEE to configure each regulators according to the selected low-power mode as described in device tree by subnodes.

See OP-TEE device tree in core/arch/arm/dts/stm32mp135f-dk.dts for configuration example:

vddcpu: buck1 {

regulator-name = "vddcpu";

regulator-min-microvolt = <1250000>;

regulator-max-microvolt = <1350000>;

regulator-always-on;

regulator-over-current-protection;

lp-stop {

regulator-suspend-microvolt = <1250000>;

};

lplv-stop {

regulator-suspend-microvolt = <900000>;

};

lplv-stop2 {

regulator-off-in-suspend;

};

standby-ddr-sr {

regulator-off-in-suspend;

};

standby-ddr-off {

regulator-off-in-suspend;

};

};

4. How to use the framework[edit | edit source]

4.1. Low-power modes[edit | edit source]

Refer to STM32MP13 reference manuals or STM32MP15 reference manuals for the full description of low-power modes.

The modes are handled by the RCC and the PWR peripherals.

Only the Suspend-to-RAM (S2RAM) target is supported for STM32MP1 series: the whole system activity is stopped and a low-power mode is entered. The software selects the deepest mode according to the activated wake-up source(s).

STM32MP1 series STMicroelectronics deliveries propose a default mapping of the low-power modes for each type of board, this default mapping can be changed thanks to the device tree as explain in a paragraph above.

4.1.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

The AN5565 STM32MP13 lines using low-power modes gives more information on these modes and on associated the wake-up sources.

The table below summarizes the device hardware states corresponding to each low-power mode.

| MPU mode | Platform mode | VDDCORE state | VDDCPU state | Clocks state |

|---|---|---|---|---|

| CRun | Run | On | On | On |

| CStop | Stop/LPLV-Stop | On/Retention | On/Retention | Off/Off |

| CStandby | Stop/LPLV-Stop/LPLVL-STOP2/Standby | On/Retention/Retention/Off | On/Retention/Off/Off | Off/Off/Off/Off |

The following tables give the list of wake-up sources available in each mode.

| Platform mode | Available wake-up sources |

|---|---|

| Stop/LP-Stop | Group1 : Group2 + HSE CSS USBH, OTG, ETH |

| LPLV-Stop LPLV-Stop2 |

Group2 : Group3 + PVD, AVD, USART, I2C, SPI, DTS, LPTIM, GPIO |

| Standby | Group3 : BOR, Vbat mon, Temp mon, LSE CSS, RTC, TAMP, Wakeup pins (from PWR) |

4.1.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

The AN5109 low-power application note also gives more information on these modes, including:

- the detailed description of the operating modes

- the low-power mode entry and exit sequences

- the low-power mode control registers

- the wake-up sources and the software mechanism that ensures the consistency between the low-power mode and the activated wake-up source

The table below summarizes the device hardware states corresponding to each low-power mode.

The term "subsystem" either refers to Arm® Cortex®-A7 (also called MPU) or to Arm® Cortex®-M4 (also called MCU). A mode prefixed by 'C' corresponds to a subsystem mode.

| Level | Mode | VDDCORE state | Subsystem Clocks state |

|---|---|---|---|

| MPU Subsystem | MPU CRun | On | On |

| MPU CStop | On | Off | |

| MPU CStandby | On | Off | |

| MCU Subsystem | MCU CRun | On | On |

| MCU CStop | On | Off |

A platform mode is the combination of MPU and MCU modes.

| MPU mode | MCU mode | Platform mode | VDDCORE state | Clocks state |

|---|---|---|---|---|

| CRun/CStop/CStandby | CRun | Run | On | On |

| CStop/CStandby | CStop | Stop (LPDS = 0) | On | Off |

| CStop/CStandby | CStop | LP-Stop or LPLV-Stop (LPDS = 1) | Retention | Off |

| CStandby | CStop MCU PDDS = 1 |

Standby | Off | Off |

The following tables give the list of wake-up sources available in each mode.

| Plaform mode | Available wake-up sources |

|---|---|

| Stop LP-Stop |

Group1 : Group2 + USB, CEC, ETH, USART, I²C, SPI, LPTIM |

| LPLV-Stop | Group2 : Group3 + PVD, AVD, GPIO |

| Standby | Group3: BOR, Vbat mon, Temp mon, LSE CSS, RTC, TAMP, Wakeup pins (from PWR) |

This list of Wake-up capability peripheral for each mode is defined in the Table 35. Functionalities depending on system operating mode of the STM32MP15 reference manuals.

5. Source code location[edit | edit source]

Below are listed the software frameworks and drivers managing the OpenSTLinux power management.

- Linux®: Linux power management

- STM32 generic power domains driver: drivers/soc/st/stm32_pm_domain.c

- STM32 MP15 cpu freq driver: drivers/cpufreq/stm32-cpufreq.c

- OP-TEE:

- PSCI and power management implementation: core/arch/arm/plat-stm32mp1/pm/

- PM framework: core/kernel/pm.c and core/include/kernel/pm.h

- For each device driver, the PM function registered by register_pm_core_service_cb()

- TF-A:

- Low-power entry, exit, DDR self refresh handling: plat/st/stm32mp1/stm32mp1_critic_power.c

- And drivers for each internal peripheral or external component are described in the associated pages:

6. How to trace and debug[edit | edit source]

See How to debug TF-A BL2 and How_to_debug_OP-TEE to activate the traces.

7. To go further[edit | edit source]

Refer to reference manual for a detailed description of low-power modes and peripheral wake-up sources:

The following application notes gives additional information on the hardware settings used for low-power management:

- AN5109 - Guidelines for using low-power modes

- AN5260 - STM32MP151/153/157 MPU lines and STPMIC1B integration on a battery powered application

- AN5284 - STM32MP1 series system power consumption

- AN5565 - STM32MP13 lines using low-power modes

- AN5587 - STM32MP13x MPU product lines and STPMIC1D / STPMIC1A integration on a wall adapter supply

- AN5787 - STM32MP13x product lines system power consumption

8. References[edit | edit source]

- ↑ Arm Power State Coordination Interface (PSCI):

https://developer.arm.com/documentation/den0022 - ↑ Arm System Control and Management Interface Platform Design Document (SCMI) specification:

https://developer.arm.com/documentation/den0056