1. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the Arm® Cortex®-A35 and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

The Arm Cortex-A35 can be instantiated several times into a single cluster:

- The STM32MP25 processor is a Cortex-A35 cluster embedding one or two core(s), depending on the selected line.

- The STM32MP23 processor is a cortex-A35 cluster embedding one or two core(s), depending on the selected line.

- The STM32MP21 processor is a cortex-A35 cluster embedding one core, depending on the selected line.

The Cortex-A35 processor is Arm's most power-efficient application processor capable of seamlessly supporting 32-bit and 64-bit code. It fully supports ARMv8-A architecture, with following features:

- AArch32 for full backward compatibility with Arm7

- AArch64 for 64-bit support

- Trustzone security

- Hardware virtualization support

- Neon Advanced SIMD and floating-point architecture support

- Memory management unit (MMU)

- Separate Level 1 (L1) data- and instruction-side memory systems

- Unified Level 2 (L2) memory system that provides Cortex-A35 subsystem memory coherency

The Cortex-A35 supports a nonsecure and a secure modes that define two hardware execution contexts, named Cortex-A35 nonsecure and Cortex-A35 secure.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

3.1. Boot time assignment[edit | edit source]

As soon as the STM32MP2 is powered up, The Cortex-A35 starts to execute the ROM code, which is the first stage of the boot chain.

With A35-TD flavor ![]() , it then executes the FSBL TF-A in secure mode before jumping to the SSBL U-Boot in nonsecure mode.

, it then executes the FSBL TF-A in secure mode before jumping to the SSBL U-Boot in nonsecure mode.

With M33-TD flavor ![]() , it then enter in low power and the Arm Cortex-M33 becomes the boot processor. As soon as the system is initialized by the Arm cortex-M33, it sends a SEV signal to wakeup the Arm cortex-A35.

, it then enter in low power and the Arm Cortex-M33 becomes the boot processor. As soon as the system is initialized by the Arm cortex-M33, it sends a SEV signal to wakeup the Arm cortex-A35.

3.1.1. On STM32MP2 series[edit | edit source]

3.1.1.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Core/Processors | Arm® Cortex®-A35 | Arm® Cortex®-A35 | ✓ | ✓ | ✓ | |

3.1.1.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Core/Processors | Arm® Cortex®-A35 | Arm® Cortex®-A35 | ✓ | ✓ | ✓ | ⬚ | Can be started by MCUboot. Running the OpenSTLinux distribution. |

3.2. Runtime assignment[edit | edit source]

The Cortex-A35 supports Cortex-A35 secure and Cortex-A35 nonsecure contexts.

With A35-TD flavor ![]() , it cannot be assigned but, it manages all the peripherals assigned to those contexts.

, it cannot be assigned but, it manages all the peripherals assigned to those contexts.

At runtime, Cortex-A35 is executing OpenSTLinux BSP distribution.

Cortex-A35 executes the secure monitor TF-A BL31 and secure OS OP-TEE in secure mode and Linux kernel in nonsecure mode

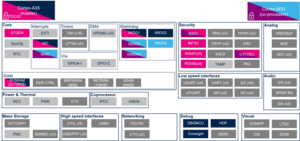

3.2.1. On STM32MP21x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP21 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Core/Processors | Arm® Cortex®-A35 | Arm® Cortex®-A35 | ✓OP-TEE ✓TF-A BL31 |

✓ | ☐ | ⬚ | In M33-TD flavor Running the OpenSTLinux distribution. |

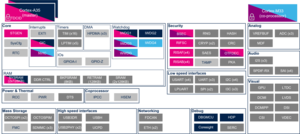

3.2.2. On STM32MP23x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP23 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Core/Processors | Arm® Cortex®-A35 | Arm® Cortex®-A35 | ✓OP-TEE ✓TF-A BL31 |

✓ | ☐ | ⬚ | In M33-TD flavor Running the OpenSTLinux distribution. |

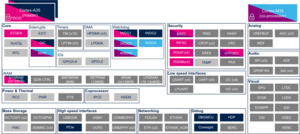

3.2.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP25 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Core/Processors | Arm® Cortex®-A35 | Arm® Cortex®-A35 | ✓OP-TEE ✓TF-A BL31 |

✓ | ☐ | ⬚ | In M33-TD flavor Running the OpenSTLinux distribution. | |

4. Software frameworks and drivers[edit | edit source]

All the software components executed by the Cortex-A35, at boot time and at runtime, constitute the OpenSTLinux distribution.

Below are listed the software frameworks and drivers managing the Arm® Cortex®-A35 for the embedded software components listed in the above tables.

- Linux®: Linux overview

- OP-TEE: OP-TEE overview

- TF-A BL2: TF-A overview and TF-A BL2 overview

- TF-A BL31: TF-A overview and TF-A BL31 overview

- U-Boot: U-Boot overview

5. How to assign and configure the peripheral[edit | edit source]

The Cortex-A35 configuration is done by the various components running on it, according to build-time parameters, and also information from the device tree.

6. How to go further[edit | edit source]

Refer to Arm website[1] for more detailed information on this core.

7. References[edit | edit source]