1. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the ETH peripheral and its main features,

- indicate the assignment of the peripheral instances at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

The ETH peripheral is based on Synopsys DesignWare® Ethernet GMAC IP, which enables the host to communicate data using the Gigabit Ethernet protocol (IEEE 802.3) at 10, 100 and 1000 Mbps.

The peripheral is composed of three main layers: the gigabit ethernet media access controller (GMAC), the MAC transaction layer (MTL), and the MAC DMA controller (MDC).

The driver used to drive the ETH is Stmmac.

The Ethernet peripheral main features are the following:

- Compliance with IEEE 802.3 specifications

- Support for IEEE 1588-2002 and IEEE 1588-2008 standards for precision networked clock synchronization

- IEEE 802.3-az for Energy Efficient Ethernet (EEE)

- IEEE 802.3x flow control automatic transmission of zero-quanta pause frame on flow control input de-assertion

- IEEE 802.1Q VLAN tag detection for reception frames

- IEEE 802.1Qbv-2015, 802.1Qbu-2016, and 802.1AS-Rev D5.0 for Time-Sensitive Networking (TSN) traffic on STM32MP25x lines

, STM32MP23x lines

, STM32MP23x lines  , STM32MP21x lines

, STM32MP21x lines  only

only - Configurability allowing to support data transfer rates of 10/100/100 Mbps, 10/100 Mbps only or 1000 Mbps only

- Support for multiple TCP/IP offload functions

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the FwST-M Package running on the Arm® Cortex®-M processor.

3.1. Boot time assignment[edit | edit source]

3.1.1. On STM32MP1 series[edit | edit source]

The Ethernet peripheral can be used at boot time by SSBL (by UBoot with tftp protocol for image loading). See How to boot the kernel via TFTP from U-Boot for more details.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 nonsecure (U-Boot) | |||

| Networking | ETH | Any instance | ☐ | Assignment (single choice) | ||

3.1.2. On STM32MP2 series[edit | edit source]

3.1.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Networking | ETH | ETH1 | ☐ | |||

| ETH2 | ☐ | |||||

3.1.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Networking | ETH | ETH1 | ☐ | ||||

| ETH2 | ☐ | ||||||

3.2. Runtime assignment[edit | edit source]

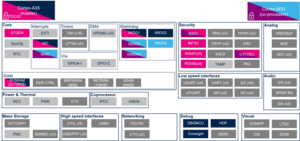

3.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP13 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) | |||

| Networking | ETH | ETH1 | ⬚ | ☐ | Assignment (single choice) |

| ETH2 | ⬚ | ☐ | Assignment (single choice) | ||

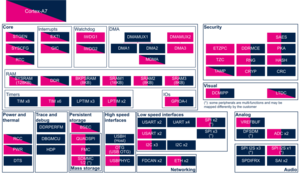

3.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Networking | ETH | ETH | ☐ | Assignment (single choice) | ||

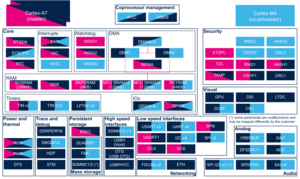

3.2.3. On STM32MP21x lines  and STM32MP23x lines

and STM32MP23x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP21 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Networking | ETH | ETH1 | ⬚OP-TEE | ☐ | ⬚ | ☐ | |

| ETH2 | ⬚OP-TEE | ☐ | ⬚ | ☐ | |||

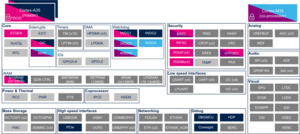

3.2.4. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP25 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Networking | ETH | ETH1 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||

| ETH2 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

4. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the ETH peripheral for the embedded software components listed in the above tables.

- Linux®: Ethernet overview

- U-Boot: U-Boot Net driver

5. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- generation of partial device trees (pin control and clock tree) for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

When the Ethernet peripheral is assigned to the Linux® OS, it is configured through the device tree according to the information given in the Ethernet device tree configuration article.