Template:ArticleMainWriter Template:ArticleApprovedVersion

SUMMARY

This article lists all internal peripherals embedded in STM32MP15 device and shows the assignment possibilities to the runtime contexts for each one of them.

Via this article, you can also access to individual peripheral articles in which information related to the overview and configuration can be found.

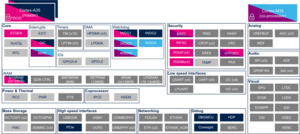

1. Internal peripherals overview[edit | edit source]

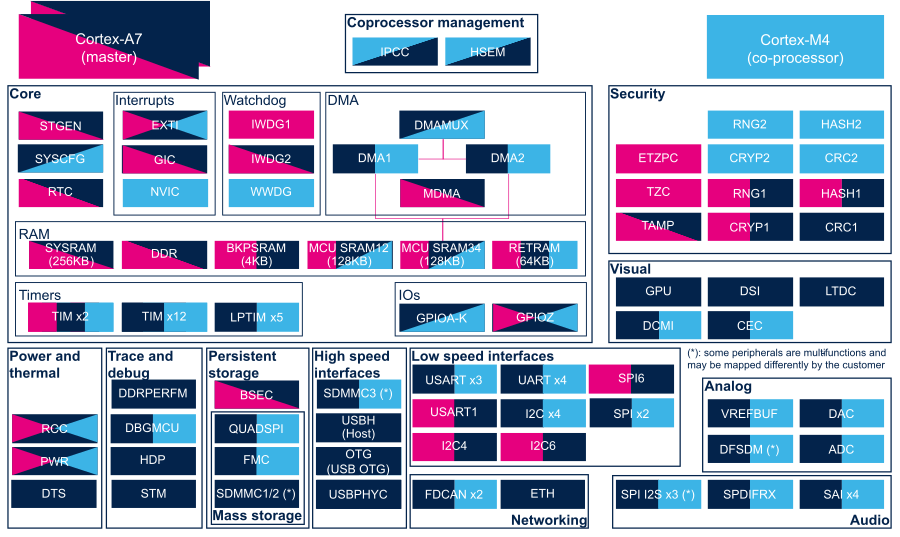

The figure below shows all peripherals embedded in STM32MP15 device, grouped per functional domains that are reused in many places of this wiki to structure the articles.

Several runtime contexts exist on STM32MP15 device[1], corresponding to the different Arm cores and associated security modes:

- Arm dual core Cortex-A7 secure (Trustzone), running a Secure Monitor or Secure OS like OP-TEE

- Arm dual core Cortex-A7 non secure , running Linux

- Arm Cortex-M4 (non-secure), running STM32Cube

Some peripherals can be strictly assigned to one runtime context: this is the case for most of the peripherals, like USART or I2C.

Other ones can be shared between several runtime contexts: this is the case for system peripherals, like PWR or RCC.

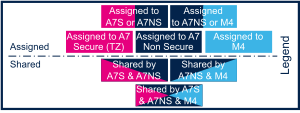

The legend below shows how assigned and shared peripherals are identified in the assignment diagram that follows:

Both the diagram below and the following summary table (in Internal peripherals assignment chapter below) are clickable in order to jump to each peripheral overview articles and get more detailed information (like software frameworks used to control them). They list STMicroelectronics recommendations. The STM32MP15 reference manual [2] may expose more possibilities than what is shown here.

2. Internal peripherals assignment[edit | edit source]

Internal peripherals assignment table template

Information about the "ADC internal peripheral" depends on the microprocessor device.

Several articles are created to manage STM32 MPU diversity and provide the appropriate level of information. Browse the one corresponding to the STM32 MPU you use.

| STM32 MPU devices | Associated articles |

|---|---|

| STM32MP13x lines |

STM32MP13 ADC internal peripheral |

| STM32MP15x lines |

STM32MP15 ADC internal peripheral |

| STM32MP2 series | STM32MP2 ADC internal peripheral |

3. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the DAC peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

4. Peripheral overview[edit | edit source]

The DAC peripheral is a voltage output digital-to-analog converter:

- It may be configured in 8- or 12-bit mode (data could be left- or right-aligned)

- It has two output channels, each with its own converter

- The dual DAC channel mode could be done independently or simultaneously

- It has built-in noise and triangle waveform generator and supports triggers for conversions, using: TIM[3], LPTIM[4] or EXTI[5]

- The DAC output buffer allows a high drive output current

- It can operate under Normal mode or low-power Sample and Hold mode (uses LSI clock, from RCC[6]).

- It may be used in conjunction with the DMA[7] controller (with underrun error detection)

- The common reference voltage, can be provided by either VREFBUF[8] or any other external regulator[9] wired to VREF+ pin.

Refer to the STM32MP15 reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

5. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

5.1. Boot time assignment[edit | edit source]

The DAC peripheral is not used at boot time.

5.2. Runtime assignment[edit | edit source]

5.2.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Analog | DAC | DAC | ☐ | ☐ | Assignment (single choice) | |

6. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the DAC peripheral for the embedded software components listed in the above tables.

- Linux®: IIO framework

- STM32Cube: HAL DAC driver

7. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

For the Linux kernel configuration, please refer to DAC device tree configuration and DAC Linux driver articles.

8. References[edit | edit source]

9. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the DFSDM peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

10. Peripheral overview[edit | edit source]

The DFSDM (Digital Filter for Sigma-Delta Modulator) peripheral is used as a generic ADC. It benefits from external analog frontend interfaces and internal digital filters.

It can be used in various applications[1] such as: audio record with MEMS microphones, energy measurement with STPMS2[2] for electricity meters or motor control...

The DFSDM peripheral provides several features, among which:

- Serial or parallel input channels:

- Digital filters, that offers up to 24-bit final ADC resolution

- Conversions that can be launched continuously, or using various triggers: by software, TIM[5], LPTIM[6], EXTI[7] or synchronously with DFSDM filter 0

- Event detectors: analog watchdog high/low thresholds, short-circuit detector, extremes detector

- Break generation to TIM[5] on analog watchdog or short-circuit detector events

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

11. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

11.1. Boot time assignment[edit | edit source]

The DFSDM peripheral is not used at boot time.

11.2. Runtime assignment[edit | edit source]

11.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) | |||

| Analog | DFSDM | DFSDM | ☐ | Assignment (single choice) | |

11.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Analog | DFSDM | DFSDM | ☐ | ☐ | Assignment (single choice) | |

12. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the DFSDM peripheral for the embedded software components listed in the above tables.

- Linux®: IIO framework or ALSA framework

- STM32Cube: HAL DFSDM driver

13. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

For the Linux kernel configuration, please refer to DFSDM device tree configuration and DFSDM Linux driver articles.

14. How to go further[edit | edit source]

See:

- STM32L4 System Digital Filter for SD Modulators interface[1], online DFSDM training with application examples from STMicroelectronics

- Getting started with sigma-delta digital interface[8], application note from STMicroelectronics

15. References[edit | edit source]

- ↑ Jump up to: 1.0 1.1 STM32L4 System Digital Filter for SD Modulators interface, online DFSDM training from STMicroelectronics

- ↑ STPMS2 "Smart sensor" device

- ↑ ADC internal peripheral

- ↑ DMA internal peripheral

- ↑ Jump up to: 5.0 5.1 TIM internal peripheral

- ↑ LPTIM internal peripheral

- ↑ EXTI internal peripheral

- ↑ Getting started with sigma-delta digital interface, application note from STMicroelectronics

Information about the "VREFBUF internal peripheral" depends on the microprocessor device.

Several articles are created to manage STM32 MPU diversity and provide the appropriate level of information. Browse the one corresponding to the STM32 MPU you use.

| STM32 MPU devices | Associated articles |

|---|---|

| STM32MP13x lines |

STM32MP13 VREFBUF internal peripheral |

| STM32MP15x lines |

STM32MP15 VREFBUF internal peripheral |

| STM32MP2 series | STM32MP2 VREFBUF internal peripheral |

16. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the SAI peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

17. Peripheral overview[edit | edit source]

The SAI (Serial Audio Interface) peripheral offers a wide set of audio protocols, such as: I2S standards (LSB or MSB-justified), PCM/DSP, TDM and S/PDIF. The SAI contains two independent audio sub-blocks. Each sub-block has its own clock generator and I/O line controller, and can be configured either as transmitter or receiver.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

18. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the FwST-M Package running on the Arm® Cortex®-M processor.

18.1. Boot time assignment[edit | edit source]

18.1.1. On STM32MP1 series[edit | edit source]

The SAI peripheral is not used at boot time.

18.1.2. On STM32MP2 series[edit | edit source]

18.1.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Audio | SAI | SAI1 | ⬚ | |||

| SAI2 | ⬚ | |||||

| SAI3 | ⬚ | |||||

| SAI4 | ⬚ | |||||

18.1.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Audio | SAI | SAI1 | ⬚ | ||||

| SAI2 | ⬚ | ||||||

| SAI3 | ⬚ | ||||||

| SAI4 | ⬚ | ||||||

18.2. Runtime assignment[edit | edit source]

18.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) | |||

| Audio | SAI | SAI1 | ☐ | Assignment (single choice) | |

| SAI2 | ☐ | Assignment (single choice) | |||

18.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Audio | SAI | SAI1 | ☐ | ☐ | Assignment (single choice) | |

| SAI2 | ☐ | ☐ | Assignment (single choice) | |||

| SAI3 | ☐ | ☐ | Assignment (single choice) | |||

| SAI4 | ☐ | ☐ | Assignment (single choice) | |||

18.2.3. On STM32MP21x lines  and STM32MP23x lines

and STM32MP23x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Audio | SAI | SAI1 | ⬚OP-TEE | ☐ | ⬚ | ☐ | |

| SAI2 | ⬚OP-TEE | ☐ | ⬚ | ☐ | |||

| SAI3 | ⬚OP-TEE | ☐ | ⬚ | ☐ | |||

| SAI4 | ⬚OP-TEE | ☐ | ⬚ | ☐ | |||

18.2.4. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Audio | SAI | SAI1 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||

| SAI2 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| SAI3 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| SAI4 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

19. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the SAI peripheral for the embedded software components listed in the above tables.

- Linux®: ALSA framework

- STM32Cube: SAI HAL driver and header file of SAI HAL module

20. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

When the Arm® Cortex®-A7 core operates in non-secure access mode, the SAI is controlled by the Linux kernel framework. Refer to SAI Linux driver to drive the SAI through Linux kernel ALSA framework. Refer to Soundcard configuration and SAI device tree configuration to configure the SAI through the Linux kernel device tree[1].

21. How to go further[edit | edit source]

STM32H7 SAI training [2] introduces the SAI features and applications. The SAI versions in STM32H7 and STM32MP1 series are very close. In consequence this training is also relevant for STM32MP1 series. The user should refer to the STM32MP13 reference manuals or STM32MP15 reference manuals for a complete description.

22. References[edit | edit source]

23. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the SPDIFRX peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

24. Peripheral overview[edit | edit source]

The SPDIFRX peripheral is designed to receive an S/PDIF flow compliant with IEC-60958 and IEC-61937. The SPDIFRX receiver provides two separated paths to retrieve the audio data and the user and channel information.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

25. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the FwST-M Package running on the Arm® Cortex®-M processor.

25.1. Boot time assignment[edit | edit source]

25.1.1. On STM32MP1 series[edit | edit source]

The SPDIFRX peripheral is not used at boot time.

25.1.2. On STM32MP2 series[edit | edit source]

25.1.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Audio | SPDIFRX | SPDIFRX | ⬚ | |||

25.1.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Audio | SPDIFRX | SPDIFRX | ⬚ | ||||

25.2. Runtime assignment[edit | edit source]

25.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) | |||

| Audio | SPDIFRX | SPDIFRX | ☐ | Assignment (single choice) | |

25.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Audio | SPDIFRX | SPDIFRX | ☐ | ☐ | Assignment (single choice) | |

25.2.3. On STM32MP21x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD).

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Audio | SPDIFRX | SPDIFRX | ⬚OP-TEE | ☐ | ⬚ | ☐ | |

25.2.4. On STM32MP23x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD).

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Audio | SPDIFRX | SPDIFRX | ⬚OP-TEE | ☐ | ⬚ | ☐ | |

25.2.5. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD).

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Audio | SPDIFRX | SPDIFRX | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||

26. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the SPDIFRX peripheral for the embedded software components listed in the above tables.

- Linux®: ALSA framework

- STM32Cube: SPDIFRX HAL driver and header file of SPDIFRX HAL module

27. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

When the Arm® Cortex®-A7 core operates in non-secure access mode, the SPDIFRX is controlled by the Linux kernel framework. Refer to the SPDIFRX Linux driver to drive the SPDIFRX through Linux kernel ALSA framework. Refer to Soundcard configuration and SPDIFRX device tree configuration to configure the SPDIFRX through Linux kernel Device tree.

28. How to go further[edit | edit source]

The STM32H7 SPDIFRX training [2], introduces the STM32 S/PDIF Receiver interface on the STM32H7. This training also applies to the STM32 MPU SPDIFRX internal peripheral.

The "Receiving S/PDIF audio stream" application note [1] describes electrical interfaces to properly connect the S/PDIF stream generated by an external device to the SPDIFRX peripheralv, for STM32F4/F7/H7 series. This application note also applies to the STM32 MPU SPDIFRX internal peripheral.

29. References[edit | edit source]

30. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the IPCC peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

31. Peripheral overview[edit | edit source]

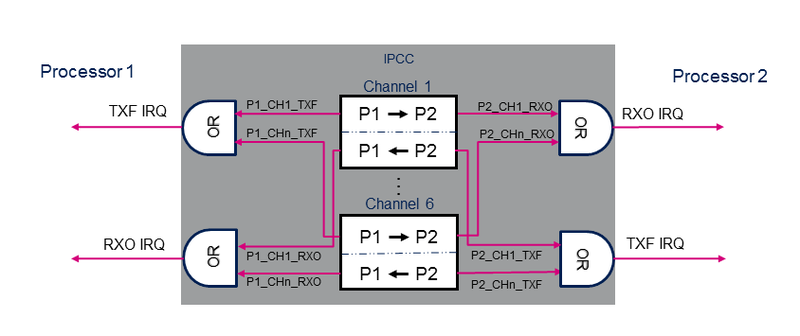

The IPCC (inter-processor communication controller) peripheral is used to exchange data between two processors. It provides a non blocking signaling mechanism to post and retrieve information in an atomic way. Note that shared memory buffers are allocated in the MCU SRAM, which is not part of the IPCC block.

The IPCC peripheral provides a hardware support to manage inter-processor communication between two processor instances. Each processor owns specific register bank and interrupts.

The IPCC provides the signaling for bidirectional channels.

Each channel is divided into two subchannels that offer a unidirectional signaling from the "sender" processor to the "receiver" processor:

- P1_TO_P2 subchannel

- P2_TO_P1 subchannel

A subchannel consists in:

- One flag that toggles between occupied and free: the flag is set to occupied by the "sender" processor and cleared by the "receiver" processor.

- Two associated interrupts (shared with the other channels):

- RXO: RX channel occupied, connected to the "receiver" processor.

- TXF: TX channel free, connected to the "sender" processor.

- Two associated interrupt masks multiplexing channel IRQs.

The IPCC supports the following channel operating modes:

- Simplex communication mode:

- Only one subchannel is used.

- Unidirectional messages: once the "sender" processor has posted the communication data in the memory, it sets the channel status flag to occupied. The "receiver" processor clears the flag when the message is treated.

- Half-duplex communication mode:

- Only one subchannel is used.

- Bidirectional messages: once the "sender" processor has posted the communication data in the memory, it sets the channel status flag to occupied. The "receiver" processor clears the flag when the message is treated and the response is available in shared memory.

- Full-duplex communication mode:

- The subchannels are used in Asynchronous mode.

- Any processor can post asynchronously a message by setting the subchannel status flag to occupied. The "receiver" processor clears the flag when the message is treated. This mode can be considered as a combination of two simplex modes on a given channel.

Refer to the reference manuals[1][2] for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

32. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the FwST-M Package running on the Arm® Cortex®-M processor.

32.1. Processor interface assignment[edit | edit source]

32.1.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

STMicroelectronics distribution uses the IPCC peripheral for inter-processor communication with the following configuration:

- The IPCC processor 1 interface (PROC1)is assigned to the Arm® Cortex®-A7, nonsecure context.

- The IPCC processor 2 interface (PROC2) is assigned to the Arm® Cortex®-M4 context.

32.1.2. On STM32MP21x lines  and STM32MP23x lines

and STM32MP23x lines  [edit | edit source]

[edit | edit source]

The IPCC1 peripheral is dedicated for the communication between the Arm® Cortex®-A35 and the Arm® Cortex®-M33. The interfaces are assigned in hardware to the Cortexes :

- The processor 1 interface (PROC1) is assigned by hardware to the Arm® Cortex®-A35, secure and nonsecure context.

- The processor 2 interface (PROC2) is assigned by hardware to the Arm® Cortex®-M33, secure and nonsecure context.

32.1.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

- The IPCC1 peripheral is dedicated for the communication between the Arm® Cortex®-A35 and the Arm® Cortex®-M33. The interfaces are assigned in hardware to the Cortexes :

- The processor 1 interface (PROC1) is assigned by hardware to the Arm® Cortex®-A35, secure and nonsecure context.

- The processor 2 interface (PROC2) is assigned by hardware to the Arm® Cortex®-M33, secure and nonsecure context.

- The IPCC2 peripheral is dedicated for the communication between the Arm® Cortex®-A35 or the Arm® Cortex®-M33 and the Arm® Cortex®-M0+.

- The processor 1 interface (PROC1) is assigned by hardware to the Arm® Cortex®-M0+.

- The processor 2 interface (PROC2) is assignable to the Arm® Cortex®-A35 or the Arm® Cortex®-M33, secure and nonsecure context.

32.2. Boot time assignment[edit | edit source]

32.2.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

The IPCC peripheral is not utilized during boot time in the OpenSTlinux distribution.

32.2.2. On STM32MP21x lines  and STM32MP23x lines

and STM32MP23x lines  [edit | edit source]

[edit | edit source]

32.2.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

The IPCC peripheral is not utilized during boot time in the OpenSTlinux distribution.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | |||

The below table shows the possible boot time allocations for the features of the IPCC1 instance.

| Feature | Boot time allocation |

Comment | ||

|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | ||

| CPU1 channel 1 | ⬚ | ⬚ | ||

| CPU1 channel 2 | ⬚ | ⬚ | ||

| CPU1 channel 3 | ⬚ | ⬚ | ||

| CPU1 channel 4 | ⬚ | ⬚ | ||

| CPU1 channel 5 | ⬚ | ⬚ | ||

| CPU1 channel 6 | ⬚ | ⬚ | ||

| CPU1 channel 7 | ⬚ | ⬚ | ||

| CPU1 channel 8 | ⬚ | ⬚ | ||

| CPU1 channel 9 | ⬚ | ⬚ | ||

| CPU1 channel 10 | ⬚ | ⬚ | ||

| CPU1 channel 11 | ⬚ | ⬚ | ||

| CPU1 channel 12 | ⬚ | ⬚ | ||

| CPU1 channel 13 | ⬚ | ⬚ | ||

| CPU1 channel 14 | ⬚ | ⬚ | ||

| CPU1 channel 15 | ⬚ | ⬚ | ||

| CPU1 channel 16 | ⬚ | ⬚ | ||

| CPU2 channel 1 | ||||

| CPU2 channel 2 | ||||

| CPU2 channel 3 | ||||

| CPU2 channel 4 | ||||

| CPU2 channel 5 | ||||

| CPU2 channel 6 | ||||

| CPU2 channel 7 | ||||

| CPU2 channel 8 | ||||

| CPU2 channel 9 | ||||

| CPU2 channel 10 | ||||

| CPU2 channel 11 | ||||

| CPU2 channel 12 | ||||

| CPU2 channel 13 | ||||

| CPU2 channel 14 | ||||

| CPU2 channel 15 | ||||

| CPU2 channel 16 | ||||

32.2.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | ||||

The below table shows the possible boot time allocations for the features of the IPCC1 instance.

| Feature | Boot time allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | ||

| CPU1 channel 1 | ⬚ | ⬚ | |||

| CPU1 channel 2 | ⬚ | ⬚ | |||

| CPU1 channel 3 | ⬚ | ⬚ | |||

| CPU1 channel 4 | ⬚ | ⬚ | |||

| CPU1 channel 5 | ⬚ | ⬚ | |||

| CPU1 channel 6 | ⬚ | ⬚ | |||

| CPU1 channel 7 | ⬚ | ⬚ | |||

| CPU1 channel 8 | ⬚ | ⬚ | |||

| CPU1 channel 9 | ⬚ | ⬚ | |||

| CPU1 channel 10 | ⬚ | ⬚ | |||

| CPU1 channel 11 | ⬚ | ⬚ | |||

| CPU1 channel 12 | ⬚ | ⬚ | |||

| CPU1 channel 13 | ⬚ | ⬚ | |||

| CPU1 channel 14 | ⬚ | ⬚ | |||

| CPU1 channel 15 | ⬚ | ⬚ | |||

| CPU1 channel 16 | ⬚ | ☑ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | ||

| CPU2 channel 1 | ⬚ | ||||

| CPU2 channel 2 | ⬚ | ||||

| CPU2 channel 3 | ⬚ | ||||

| CPU2 channel 4 | ⬚ | ||||

| CPU2 channel 5 | ⬚ | ||||

| CPU2 channel 6 | ⬚ | ||||

| CPU2 channel 7 | ⬚ | ||||

| CPU2 channel 8 | ⬚ | ||||

| CPU2 channel 9 | ⬚ | ||||

| CPU2 channel 10 | ⬚ | ||||

| CPU2 channel 11 | ⬚ | ||||

| CPU2 channel 12 | ⬚ | ||||

| CPU2 channel 13 | ⬚ | ||||

| CPU2 channel 14 | ⬚ | ||||

| CPU2 channel 15 | ⬚ | ||||

| CPU2 channel 16 | ☑ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | |||

32.2.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

32.2.3.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

The IPCC peripherals are not utilized during boot time in the OpenSTlinux distribution.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | |||

| IPCC2 | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | |||||

The below table shows the possible boot time allocations for the features of the IPCC1 instance.

| Feature | Boot time allocation |

Comment | ||

|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | ||

| CPU1 channel 1 | ⬚ | ⬚ | ||

| CPU1 channel 2 | ⬚ | ⬚ | ||

| CPU1 channel 3 | ⬚ | ⬚ | ||

| CPU1 channel 4 | ⬚ | ⬚ | ||

| CPU1 channel 5 | ⬚ | ⬚ | ||

| CPU1 channel 6 | ⬚ | ⬚ | ||

| CPU1 channel 7 | ⬚ | ⬚ | ||

| CPU1 channel 8 | ⬚ | ⬚ | ||

| CPU1 channel 9 | ⬚ | ⬚ | ||

| CPU1 channel 10 | ⬚ | ⬚ | ||

| CPU1 channel 11 | ⬚ | ⬚ | ||

| CPU1 channel 12 | ⬚ | ⬚ | ||

| CPU1 channel 13 | ⬚ | ⬚ | ||

| CPU1 channel 14 | ⬚ | ⬚ | ||

| CPU1 channel 15 | ⬚ | ⬚ | ||

| CPU1 channel 16 | ⬚ | ⬚ | ||

| CPU2 channel 1 | ||||

| CPU2 channel 2 | ||||

| CPU2 channel 3 | ||||

| CPU2 channel 4 | ||||

| CPU2 channel 5 | ||||

| CPU2 channel 6 | ||||

| CPU2 channel 7 | ||||

| CPU2 channel 8 | ||||

| CPU2 channel 9 | ||||

| CPU2 channel 10 | ||||

| CPU2 channel 11 | ||||

| CPU2 channel 12 | ||||

| CPU2 channel 13 | ||||

| CPU2 channel 14 | ||||

| CPU2 channel 15 | ||||

| CPU2 channel 16 | ||||

The below table shows the possible boot time allocations for the features of the IPCC2 instance.

| Feature | Boot time allocation |

Comment | ||

|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | ||

| CPU1 channel 1 | ⬚ | ⬚ | ||

| CPU1 channel 2 | ⬚ | ⬚ | ||

| CPU1 channel 3 | ⬚ | ⬚ | ||

| CPU1 channel 4 | ⬚ | ⬚ | ||

| CPU2 channel 1 | ||||

| CPU2 channel 2 | ||||

| CPU2 channel 3 | ||||

| CPU2 channel 4 | ||||

32.2.3.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | ||||

| IPCC2 | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | ||||||

The below table shows the possible boot time allocations for the features of the IPCC1 instance.

| Feature | Boot time allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | ||

| CPU1 channel 1 | ⬚ | ⬚ | |||

| CPU1 channel 2 | ⬚ | ⬚ | |||

| CPU1 channel 3 | ⬚ | ⬚ | |||

| CPU1 channel 4 | ⬚ | ⬚ | |||

| CPU1 channel 5 | ⬚ | ⬚ | |||

| CPU1 channel 6 | ⬚ | ⬚ | |||

| CPU1 channel 7 | ⬚ | ⬚ | |||

| CPU1 channel 8 | ⬚ | ⬚ | |||

| CPU1 channel 9 | ⬚ | ⬚ | |||

| CPU1 channel 10 | ⬚ | ⬚ | |||

| CPU1 channel 11 | ⬚ | ⬚ | |||

| CPU1 channel 12 | ⬚ | ⬚ | |||

| CPU1 channel 13 | ⬚ | ⬚ | |||

| CPU1 channel 14 | ⬚ | ⬚ | |||

| CPU1 channel 15 | ⬚ | ⬚ | |||

| CPU1 channel 16 | ⬚ | ☑ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | ||

| CPU2 channel 1 | ⬚ | ||||

| CPU2 channel 2 | ⬚ | ||||

| CPU2 channel 3 | ⬚ | ||||

| CPU2 channel 4 | ⬚ | ||||

| CPU2 channel 5 | ⬚ | ||||

| CPU2 channel 6 | ⬚ | ||||

| CPU2 channel 7 | ⬚ | ||||

| CPU2 channel 8 | ⬚ | ||||

| CPU2 channel 9 | ⬚ | ||||

| CPU2 channel 10 | ⬚ | ||||

| CPU2 channel 11 | ⬚ | ||||

| CPU2 channel 12 | ⬚ | ||||

| CPU2 channel 13 | ⬚ | ||||

| CPU2 channel 14 | ⬚ | ||||

| CPU2 channel 15 | ⬚ | ||||

| CPU2 channel 16 | ☑ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | |||

The below table shows the possible boot time allocations for the features of the IPCC2 instance.

| Feature | Boot time allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | ||

| CPU1 channel 1 | ⬚ | ⬚ | ⬚ | ||

| CPU1 channel 2 | ⬚ | ⬚ | ⬚ | ||

| CPU1 channel 3 | ⬚ | ⬚ | ⬚ | ||

| CPU1 channel 4 | ⬚ | ⬚ | ⬚ | ||

| CPU2 channel 1 | |||||

| CPU2 channel 2 | |||||

| CPU2 channel 3 | |||||

| CPU2 channel 4 | |||||

32.3. Runtime assignment[edit | edit source]

It does not make sense to allocate the IPCC to a single runtime execution context. It is consequently enabled by default for both cores in the STM32CubeMX.

32.3.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Coprocessor | IPCC | IPCC | ☑ | ☑ | Shared (none or both) | |

| Processor interface | Context | Comment | ||

|---|---|---|---|---|

| Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| PROC1 channel 1 | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| PROC1 channel 2 | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| PROC1 channel 3 | ☑ | Simplex communication used by the remote framework to request the Cortex-M4 to shutdown. | ||

| PROC1 channel 4 | ☐ | |||

| PROC1 channel 5 | ☐ | |||

| PROC1 channel 6 | ☐ | |||

| PROC2 channel 1 | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| PROC2 channel 2 | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| PROC2 channel 3 | ☑ | Simplex communication used by the remote framework to request the Cortex-M4 to shutdown. | ||

| PROC2 channel 4 | ☐ | |||

| PROC2 channel 5 | ☐ | |||

| PROC2 channel 6 | ☐ | |||

32.3.2. On STM32MP21x lines  and STM32MP23x lines

and STM32MP23x lines  [edit | edit source]

[edit | edit source]

32.3.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | ||||

The below table shows the possible runtime allocations for the features of the IPCC1 instance.

| Feature | Runtime allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | ||

| CPU1 channel 1 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| CPU1 channel 2 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| CPU1 channel 3 | ☐OP-TEE | ☑ | Simplex communication used by the remote framework to request the Cortex-M33 to shutdown. | ||

| CPU1 channel 4 | ☐OP-TEE | ☐ | |||

| CPU1 channel 5 | ☐OP-TEE | ☐ | |||

| CPU1 channel 6 | ☐OP-TEE | ☐ | |||

| CPU1 channel 7 | ☐OP-TEE | ☐ | |||

| CPU1 channel 8 | ☐OP-TEE | ☐ | |||

| CPU1 channel 9 | ☐OP-TEE | ☐ | |||

| CPU1 channel 10 | ☐OP-TEE | ☐ | |||

| CPU1 channel 11 | ☐OP-TEE | ☐ | |||

| CPU1 channel 12 | ☐OP-TEE | ☐ | |||

| CPU1 channel 13 | ☐OP-TEE | ☐ | |||

| CPU1 channel 14 | ☐OP-TEE | ☐ | |||

| CPU1 channel 15 | ☐OP-TEE | ☐ | |||

| CPU1 channel 16 | ☑OP-TEE | ☐ | SCMI for system resource configuration controlled by the Cortex-A35 secure (OPTEE) | ||

| CPU2 channel 1 | ☐ | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| CPU2 channel 2 | ☐ | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| CPU2 channel 3 | ☐ | ☑ | Simplex communication used by the remote framework to request the Cortex-M4 to shutdown. | ||

| CPU2 channel 4 | ☐ | ☐ | |||

| CPU2 channel 5 | ☐ | ☐ | |||

| CPU2 channel 6 | ☐ | ☐ | |||

| CPU2 channel 7 | ☐ | ☐ | |||

| CPU2 channel 8 | ☐ | ☐ | |||

| CPU2 channel 9 | ☐ | ☐ | |||

| CPU2 channel 10 | ☐ | ☐ | |||

| CPU2 channel 11 | ☐ | ☐ | |||

| CPU2 channel 12 | ☐ | ☐ | |||

| CPU2 channel 13 | ☐ | ☐ | |||

| CPU2 channel 14 | ☐ | ☐ | |||

| CPU2 channel 15 | ☐ | ☐ | |||

| CPU2 channel 16 | ☐ | ☑ | SCMI for system resource configuration controlled by the Cortex-A35 secure (OPTEE) | ||

32.3.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | ||||

The below table shows the possible runtime allocations for the features of the IPCC1 instance.

| Feature | Runtime allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | ||

| CPU1 channel 1 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| CPU1 channel 2 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| CPU1 channel 3 | ☐OP-TEE | ☑ | Simplex communication used by the remote framework to request the Cortex-M33 to shutdown. | ||

| CPU1 channel 4 | ☐OP-TEE | ☐ | |||

| CPU1 channel 5 | ☐OP-TEE | ☐ | |||

| CPU1 channel 6 | ☐OP-TEE | ☐ | |||

| CPU1 channel 7 | ☐OP-TEE | ☐ | |||

| CPU1 channel 8 | ☐OP-TEE | ☐ | |||

| CPU1 channel 9 | ☐OP-TEE | ☐ | |||

| CPU1 channel 10 | ☐OP-TEE | ☐ | |||

| CPU1 channel 11 | ☐OP-TEE | ☐ | |||

| CPU1 channel 12 | ☐OP-TEE | ☐ | |||

| CPU1 channel 13 | ☐OP-TEE | ☐ | |||

| CPU1 channel 14 | ☑TF-A | ☐ | PSA service for platform secure architecture service controlled by the Cortex-M33 secure (TF-M) | ||

| CPU1 channel 15 | ☑OP-TEE | ☐ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | ||

| CPU1 channel 16 | ☐OP-TEE | ☑ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | ||

| CPU2 channel 1 | ☐ | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| CPU2 channel 2 | ☐ | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| CPU2 channel 3 | ☐ | ☑ | Simplex communication used by the remote framework to request the Cortex-M4 to shutdown. | ||

| CPU2 channel 4 | ☐ | ☐ | |||

| CPU2 channel 5 | ☐ | ☐ | |||

| CPU2 channel 6 | ☐ | ☐ | |||

| CPU2 channel 7 | ☐ | ☐ | |||

| CPU2 channel 8 | ☐ | ☐ | |||

| CPU2 channel 9 | ☐ | ☐ | |||

| CPU2 channel 10 | ☐ | ☐ | |||

| CPU2 channel 11 | ☐ | ☐ | |||

| CPU2 channel 12 | ☐ | ☐ | |||

| CPU2 channel 13 | ☐ | ☐ | |||

| CPU2 channel 14 | ☑ | ☐ | PSA service for platform secure architecture service controlled by the Cortex-M33 secure (TF-M) | ||

| CPU2 channel 15 | ☑ | ☐ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | ||

| CPU2 channel 16 | ☑ | ☐ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | ||

32.3.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

32.3.3.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | |||||

| IPCC2 | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | |||||||

The below table shows the possible runtime allocations for the features of the IPCC1 instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| CPU1 channel 1 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| |||

| CPU1 channel 2 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| |||

| CPU1 channel 3 | ☐OP-TEE | ☑ | Simplex communication used by the remote framework to request the Cortex-M33 to shutdown. | |||

| CPU1 channel 4 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 5 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 6 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 7 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 8 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 9 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 10 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 11 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 12 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 13 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 14 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 15 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 16 | ☑OP-TEE | ☐ | SCMI for system resource configuration controlled by the Cortex-A35 secure (OPTEE) | |||

| CPU2 channel 1 | ☐ | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| |||

| CPU2 channel 2 | ☐ | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| |||

| CPU2 channel 3 | ☐ | ☑ | Simplex communication used by the remote framework to request the Cortex-M33 to shutdown. | |||

| CPU2 channel 4 | ☐ | ☐ | ||||

| CPU2 channel 5 | ☐ | ☐ | ||||

| CPU2 channel 6 | ☐ | ☐ | ||||

| CPU2 channel 7 | ☐ | ☐ | ||||

| CPU2 channel 8 | ☐ | ☐ | ||||

| CPU2 channel 9 | ☐ | ☐ | ||||

| CPU2 channel 10 | ☐ | ☐ | ||||

| CPU2 channel 11 | ☐ | ☐ | ||||

| CPU2 channel 12 | ☐ | ☐ | ||||

| CPU2 channel 13 | ☐ | ☐ | ||||

| CPU2 channel 14 | ☐ | ☐ | ||||

| CPU2 channel 15 | ☐ | ☐ | ||||

| CPU2 channel 16 | ☐ | ☑ | SCMI for system resource configuration controlled by the Cortex-A35 secure (OPTEE) | |||

The below table shows the possible runtime allocations for the features of the IPCC2 instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| CPU1 channel 1 | ☐OP-TEE | ☑ | ☐ | ☐ | Interprocessor communication | |

| CPU1 channel 2 | ☐OP-TEE | ☑ | ☐ | ☐ | Simplex communication used by the remote framework to request the Cortex-M0+ to shutdown. | |

| CPU1 channel 3 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| CPU1 channel 4 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| CPU2 channel 1 | ☑ | Interprocessor communication | ||||

| CPU2 channel 2 | ☑ | Simplex communication used by the remote framework to request the Cortex-M0+ to shutdown. | ||||

| CPU2 channel 3 | ☐ | |||||

| CPU2 channel 4 | ☐ | |||||

32.3.3.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Coprocessor | IPCC |

IPCC1 | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | |||||

| IPCC2 | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | |||||||

The below table shows the possible runtime allocations for the features of the IPCC1 instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| CPU1 channel 1 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| |||

| CPU1 channel 2 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| |||

| CPU1 channel 3 | ☐OP-TEE | ☑ | Simplex communication used by the remote framework to request the Cortex-A to shutdown. | |||

| CPU1 channel 4 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 5 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 6 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 7 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 8 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 9 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 10 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 11 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 12 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 13 | ☐OP-TEE | ☐ | ||||

| CPU1 channel 14 | ☑TF-A | ☐ | PSA service for platform secure architecture service controlled by the Cortex-M33 secure (TF-M) | |||

| CPU1 channel 15 | ☑TF-A | ☐ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | |||

| CPU1 channel 16 | ☐OP-TEE | ☑ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | |||

| CPU2 channel 1 | ☐ | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| |||

| CPU2 channel 2 | ☐ | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| |||

| CPU2 channel 3 | ☐ | ☑ | Simplex communication used by the remote framework to request the Cortex-A to shutdown. | |||

| CPU2 channel 4 | ☐ | ☐ | ||||

| CPU2 channel 5 | ☐ | ☐ | ||||

| CPU2 channel 6 | ☐ | ☐ | ||||

| CPU2 channel 7 | ☐ | ☐ | ||||

| CPU2 channel 8 | ☐ | ☐ | ||||

| CPU2 channel 9 | ☐ | ☐ | ||||

| CPU2 channel 10 | ☐ | ☐ | ||||

| CPU2 channel 11 | ☐ | ☐ | ||||

| CPU2 channel 12 | ☐ | ☐ | ||||

| CPU2 channel 13 | ☐ | ☐ | ||||

| CPU2 channel 14 | ☑ | ☐ | PSA service for platform secure architecture service controlled by the Cortex-M33 secure (TF-M) | |||

| CPU2 channel 15 | ☑ | ☐ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | |||

| CPU2 channel 16 | ☑ | ☐ | SCMI for system resource configuration controlled by the Cortex-M33 secure (TF-M) | |||

The below table shows the possible runtime allocations for the features of the IPCC2 instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| CPU1 channel 1 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| CPU1 channel 2 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| CPU1 channel 3 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| CPU1 channel 4 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| CPU2 channel 1 | ☐ | |||||

| CPU2 channel 2 | ☐ | |||||

| CPU2 channel 3 | ☐ | |||||

| CPU2 channel 4 | ☐ | |||||

33. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the IPCC peripheral for the embedded software components listed in the above tables.

- Linux®: mailbox framework

- STM32Cube: IPCC HAL driver and header file of IPCC HAL module

34. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.The IPCC peripheral is shared between the Arm Cortex-A and Cortex-M contexts. A particular attention must therefore be paid to have a complementary configuration on both contexts.

35. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the HSEM peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

36. Peripheral overview[edit | edit source]

The HSEM (hardware spinlock) peripheral is used to provide synchronization and mutual exclusion between heterogeneous processors.

- 32 hardware semaphores are available on the platform.

- semaphores could be accessed by the Arm® Cortex®-A7 core and the Arm® Cortex®-M4

Refer to the STM32MP15 reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

37. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

37.1. Boot time assignment[edit | edit source]

37.1.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

The hardware semaphore is used at boot time for GPIO access protection between the Arm® Cortex®-A7 and Cortex®-M4 cores. See Protecting GPIO and EXTI system resources by hardware semaphores for details.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 nonsecure (U-Boot) | |||

| Coprocessor | HSEM | HSEM | ☐ | |||

37.2. Runtime assignment[edit | edit source]

37.2.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

It does not make sense to allocate HSEM to a single runtime execution context, that is why it is enabled by default for both cores in the STM32CubeMX.

The hardware semaphore is used at runtime for GPIO and EXTI access protection between the Arm® Cortex®-A7 and Cortex®-M4 cores. See Protecting GPIO and EXTI system resources by hardware semaphores for details.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Coprocessor | HSEM | HSEM | ⬚ | ☑ | ☑ | |

38. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the HSEM peripheral for the embedded software components listed in the above tables.

- Linux®: hardware spinlock framework

- STM32Cube: HSEM HAL driver and header file of HSEM HAL module

39. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

The HSEM peripheral is shared between the Cortex-A and Cortex-M contexts, so a particular attention must be paid to have a complementary configuration on both contexts.

40. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the RTC peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

41. Peripheral overview[edit | edit source]

The RTC peripheral is used to provide the date and clock to the application. It supports programmable alarms and wake up capabilities.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

42. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the FwST-M Package running on the Arm® Cortex®-M processor.

42.1. Boot time assignment[edit | edit source]

42.1.1. On STM32MP1 series[edit | edit source]

By default after a backup domain power-on reset (performed at boot time), all RTC registers can be read or written in both secure and non-secure modes.

In OpenSTLinux distribution, the first stage bootloader (FSBL, running in secure mode) keeps this default configuration, leaving full control to Linux® at runtime.

The RTC peripheral is able to generate two interrupts:

- A secure interrupt, connected to the Arm® Cortex®-A7 GIC, not used in OpenSTLinux distribution.

- A non-secure interrupt, connected both to Arm® Cortex®-A7 GIC and Cortex-M4 NVIC (STM32MP15x lines

only): this interrupt is used on Linux® and by default in OpenSTLinux distribution.

only): this interrupt is used on Linux® and by default in OpenSTLinux distribution.

The RTC peripheral is part of the backup domain which reset and clock are controlled via the RCC by the first stage bootloader (FSBL, running in secure mode) at boot time.

The RTC reset occurs when the backup domain is reset. To avoid clearing the TAMP register contents, this is only done on cold boot, not on wake up.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 nonsecure (U-Boot) | |||

| Core | RTC | RTC | ⬚ | ☐ | ||

42.1.2. On STM32MP2 series[edit | edit source]

42.1.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Core | RTC |

RTC | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | |||

The below table shows the possible boot time allocations for the features of the RTC instance.

| Feature | Boot time allocation |

Comment | ||

|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | ||

| Alarm A | ⬚ | ☐ | ||

| Alarm B | ⬚ | ⬚ | ||

| Wakeup timer | ⬚ | ☐ | ||

| Timestamp | ⬚ | ☐ | ||

| Calibration | ⬚ | ☐ | ||

| Initialization | ⬚ | ☐ | ||

42.1.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Core | RTC |

RTC | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | ||||

The below table shows the possible boot time allocations for the features of the RTC instance.

| Feature | Boot time allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | ||

| Alarm A | ⬚ | ☐ | ⬚ | ||

| Alarm B | ⬚ | ⬚ | ⬚ | ||

| Wakeup timer | ⬚ | ☐ | ⬚ | ||

| Timestamp | ⬚ | ☐ | ⬚ | ||

| Calibration | ⬚ | ☐ | ⬚ | ||

| Initialization | ⬚ | ☐ | ⬚ | ||

42.2. Runtime assignment[edit | edit source]

42.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) | |||

| Core | RTC | RTC | ☑ | ☐ | RTC is mandatory to resynchronize STGEN after exiting low-power modes. |

42.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core | RTC | RTC | ☑ | ☐ | ☐ | RTC is mandatory to resynchronize STGEN after exiting low-power modes. |

42.2.3. On STM32MP21x lines  and STM32MP23x lines

and STM32MP23x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Core | RTC |

RTC | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | RTC is mandatory to resynchronize STGEN after exiting low-power modes. | |||

The below table shows the possible runtime allocations for the features of the RTC instance.

| Feature | Runtime allocation |

Comment | |||

|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | ||

| Alarm A | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | |

| Alarm B | ⬚TF-A BL31 ⬚OP-TEE |

⬚ | ⬚ | ☐ | |

| Wakeup timer | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | |

| Timestamp | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | |

| Calibration | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | |

| Initialization | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | |

42.2.4. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Core | RTC |

RTC | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | RTC is mandatory to resynchronize STGEN after exiting low-power modes. | ||||

The below table shows the possible runtime allocations for the features of the RTC instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| Alarm A | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | ☐ | |

| Alarm B | ⬚TF-A BL31 ⬚OP-TEE |

⬚ | ⬚ | ☐ | ☐ | |

| Wakeup timer | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | ☐ | |

| Timestamp | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | ☐ | |

| Calibration | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | ☐ | |

| Initialization | ⬚TF-A BL31 ☐OP-TEE |

☐ | ⬚ | ☐ | ☐ | |

43. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the RTC peripheral for the embedded software components listed in the above tables.

- Linux®: RTC framework

- U-Boot:

- OP-TEE:

44. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

For Linux kernel configuration, please refer to RTC device tree configuration.

45. Article purpose[edit | edit source]

The purpose of this article is to:

- Briefly introduce the STGEN peripheral and its main features.

- Indicate the peripheral instance assignments at boot time and runtime (including whether instances can be allocated to secure contexts).

- List the software frameworks and drivers managing the peripheral.

- Explain how to configure the peripheral.

46. Peripheral overview[edit | edit source]

The STGEN peripheral provides the reference clock used by the Arm® Cortex®-Axxx generic timer [1]for its counters, including the system tick generation.

It is clocked by either the HSI (High Speed Internal) oscillator or the HSE (High Speed External) oscillator. During the boot phase, STGEN is clocked by HSI until HSE is set up. This should be done at an early stage. Caution is needed when switching from one source to another, as the STGEN counter must be updated according to the new frequency. Otherwise, the time reference will be incorrect.

The STGEN is a single-instance peripheral that can be accessed via the following two register sets:

- STGENC for control: the secure port.

- STGENR for read-only access: the nonsecure port.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced in chapter 4 below, to see which features are implemented.

On Arm 64-bit platforms, the update of the Arm CPU counter register can only be done by the highest exception level, which is TF-A BL31 on the STM32MP2 series.

47. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s).

47.1. Boot time assignment[edit | edit source]

47.1.1. On STM32MP1 series[edit | edit source]

The STGEN is first initialized by the ROM code, then updated by the FSBL (see Boot chain overview) once the HSE clock is set up.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 nonsecure (U-Boot) | |||

| Core | STGEN | STGEN | ✓ | ✓ | ||

47.1.2. On STM32MP2 series[edit | edit source]

47.1.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Core | STGEN | STGEN | ✓ | ☑ | Read-only (STGENR) |

|

47.1.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Core | STGEN | STGEN | ✓ | ☑ | Read-only (STGENR) |

||

47.2. Runtime assignment[edit | edit source]

47.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) | |||

| Core | STGEN | STGEN | ✓ | ||

47.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core | STGEN | STGEN | ✓ | |||

47.2.3. On STM32MP21x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Core | STGEN | STGEN | ☑OP-TEE ☑TF-A BL31 |

Read-only (STGENR) |

|||

47.2.4. On STM32MP23x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Core | STGEN | STGEN | ☑OP-TEE ☑TF-A BL31 |

Read-only (STGENR) |

|||

47.2.5. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Core | STGEN | STGEN | ☑OP-TEE ☑TF-A BL31 |

Read-only (STGENR) |

||||

48. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the STGEN peripheral for the embedded software components listed in the above tables.

Linux®/U-Boot use the Arm® Cortex®-Axxx generic timer that gets its counter from the STGEN, but this is transparent at runtime. Therefore, there is no noticeable framework or driver for these components.

48.1. STM32MP1 series[edit | edit source]

In OP-TEE, the STGEN's counter value is saved/restored during low-power sequences to keep platform time coherence. The STGEN configuration is done by TF-A. The frequency of the counter is restored in TF-A as well.

48.2. STM32MP2 series[edit | edit source]

The STGEN configuration/restore is done by OP-TEE and the Arm counter frequency is set by TF-A BL31 upon receiving a specific SMC call from OP-TEE.

48.3. Sources[edit | edit source]

- TF-A:

- drivers/st/clk/stm32mp_clkfunc.c STGEN configuration and frequency restoration

- plat/st/stm32mp2/services/stgen_svc.c STGEN service in BL31 for STM32MP2 series

- OP-TEE:

- core/arch/arm/plat-stm32mp1/pm/context.c : Save STGEN value in pm context during low power

- core/drivers/counter/stm32_stgen.c : STGEN driver for STM32MP2 series

49. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and completed manually, if necessary).

This tool can also be used to configure the peripheral:

- Partial device tree (pin control and clock tree) generation for the OpenSTLinux software components.

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context to which the peripheral is assigned.