Registered User mNo edit summary |

Registered User No edit summary |

||

| (2 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{ApplicableFor | |||

|MPUs list= STM32MP13x | |MPUs list=STM32MP13x | ||

|MPUs checklist=STM32MP13x, STM32MP15x, STM32MP25x | |MPUs checklist=STM32MP13x, STM32MP15x, STM32MP21x, STM32MP23x, STM32MP25x | ||

}}</noinclude> | }} | ||

<noinclude></noinclude> | |||

This article lists all internal peripherals embedded in {{MicroprocessorDevice | device=13}} and shows the assignment possibilities to the execution contexts for each one of them.<br> | This article lists all internal peripherals embedded in {{MicroprocessorDevice | device=13}} and shows the assignment possibilities to the execution contexts for each one of them.<br> | ||

From this article, you can also access to individual peripheral articles with information related to the overview and configuration aspects. | From this article, you can also access to individual peripheral articles with information related to the overview and configuration aspects. | ||

{{ReviewsComments|-- [[User:Jean Christophe Trotin|Jean Christophe Trotin]] ([[User talk:Jean Christophe Trotin|talk]]) 11:11, 23 November 2023 (CET)<br />Several points: | |||

* Why not writing "For the STM32CubeMP13 Package (running on the Arm<sup>®</sup> Cortex<sup>®</sup>-A7 processor), [...]" instead of "For the STM32Cube MPU package (such as e.g. STM32CubeMP13)", since the article is dedicated to the MP13 | |||

* If I correctly understand, the assignment of the peripherals is the same as the one indicated in the "OP-TEE" column. But, if, in the "OP-TEE" column, it is written that the peripherals is not assigned to the secure context (e.g. TIM 1 to 8), does it mean that there are also not assigned in the STM32CubeMP13 Package case (does it mean that there are not usable?)? | |||

* I'm wondering if the point wouldn't be to say for the STM32CubeMP13 Package that all the supported peripherals are assigned to the secure context, and it is possible to assign them to the non-secure context thanks to STM32CubeMX? <br> NSA : AP loic could you please check which of sentences proposed below illustrate in the best manner the situaiton }} | |||

{{Important| This article has be written in scope of STM32 MPU OpenSTLinux Embedded software. <br> | |||

For the STM32CubeMP13 Package (running on the Arm<sup>®</sup> Cortex<sup>®</sup>-A7 processor), the [[#Internal peripherals assignment| peripheral assignment table]] is also applicable. <br>All supported peripherals are, by default, assigned to the secure context, and it is possible to assign them to the non-secure context thanks to STM32CubeMX. <br> or <br>The default peripheral assignments for STM32CubeMP13 are described in Arm<sup>®</sup> Cortex<sup>®</sup>-A secure column of this table. As usual, the customer can change this configuration to switch in Arm<sup>®</sup> Cortex<sup>®</sup>-A non-secure context using STM32CubeMX}} | |||

{{ReviewsComments|-- [[User:Loic Pallardy|Loic Pallardy]] ([[User talk:Loic Pallardy|talk]]) 21:55, 23 November 2023 (CET)<br />agree with Jean Christophe: | |||

* need to mention Cortex-A Cube package else it could be confusing even if this page is MP13 only | |||

* in fact we should have a page that describe CA7 Cube content which allows to create a monolothic firmware running in one execution context | |||

* Cube firmware can run either on CA7 secure context or CA7 non-secure context depending on customer choice | |||

* CubeMX allows to assign/enable peripherals that will be handled by Cube firmware | |||

* so default assignment shown below is not valid, all choices are ...}} | |||

==Internal peripherals overview== | ==Internal peripherals overview== | ||

| Line 12: | Line 28: | ||

Several '''execution contexts''' exist on {{MicroprocessorDevice | device=13}}<ref>[[:Category:STM32_MPU_microprocessor_devices#Multiple-core_architecture_concepts|STM32 MPU microprocessor devices: multiple-core architecture concepts]]</ref>, corresponding to the '''Arm Cortex-A7 security modes''': | Several '''execution contexts''' exist on {{MicroprocessorDevice | device=13}}<ref>[[:Category:STM32_MPU_microprocessor_devices#Multiple-core_architecture_concepts|STM32 MPU microprocessor devices: multiple-core architecture concepts]]</ref>, corresponding to the '''Arm Cortex-A7 security modes''': | ||

* <span style="color:#FFFFFF; background:{{STPink}};"> Arm Cortex-A7 secure </span> (Trustzone), running [[STM32 MPU ROM code overview|ROM code]] and [[TF-A BL2 overview|TF-A BL2]] at boot time, and running [[OP-TEE overview|OP-TEE]] at runtime | * <span style="color:#FFFFFF; background:{{STPink}};"> Arm Cortex-A7 secure </span> (Trustzone), running [[STM32 MPU ROM code overview|ROM code]] and [[TF-A BL2 overview|TF-A BL2]] at boot time, and running [[STM32 MPU OP-TEE overview|OP-TEE]] at runtime | ||

* <span style="color:#FFFFFF; background:{{STDarkBlue}};"> Arm Cortex-A7 non secure </span>, running [[U-Boot overview|U-Boot]] at boot time, and running [[STM32MP13 Linux kernel overview|Linux]] at runtime | * <span style="color:#FFFFFF; background:{{STDarkBlue}};"> Arm Cortex-A7 non secure </span>, running [[U-Boot overview|U-Boot]] at boot time, and running [[STM32MP13 Linux kernel overview|Linux]] at runtime | ||

Latest revision as of 15:19, 7 October 2024

This article lists all internal peripherals embedded in STM32MP13x lines ![]() and shows the assignment possibilities to the execution contexts for each one of them.

and shows the assignment possibilities to the execution contexts for each one of them.

From this article, you can also access to individual peripheral articles with information related to the overview and configuration aspects.

1. Internal peripherals overview[edit | edit source]

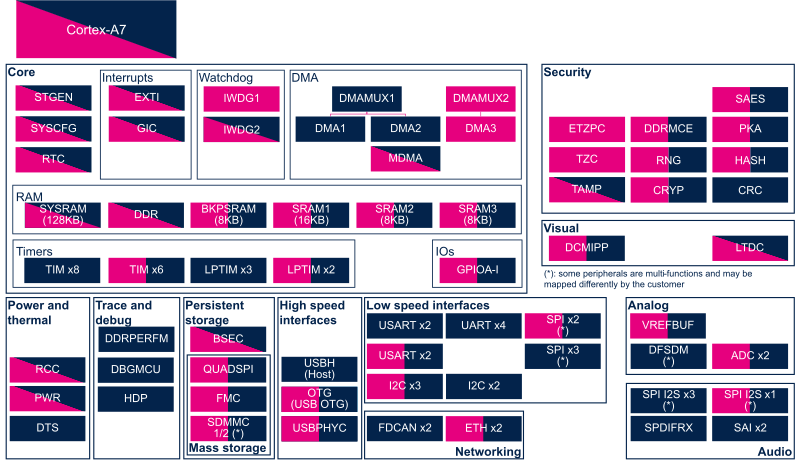

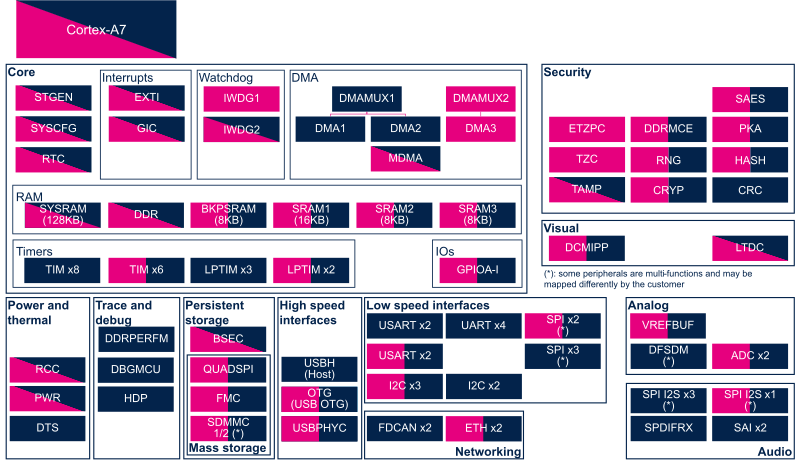

The figure below shows all peripherals embedded in STM32MP13x lines ![]() , grouped per functional domains that are reused in many places of this wiki to structure the articles.

, grouped per functional domains that are reused in many places of this wiki to structure the articles.

Several execution contexts exist on STM32MP13x lines ![]() [1], corresponding to the Arm Cortex-A7 security modes:

[1], corresponding to the Arm Cortex-A7 security modes:

- Arm Cortex-A7 secure (Trustzone), running ROM code and TF-A BL2 at boot time, and running OP-TEE at runtime

- Arm Cortex-A7 non secure , running U-Boot at boot time, and running Linux at runtime

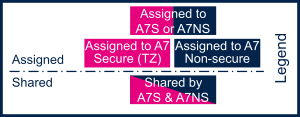

Some peripherals can be strictly assigned to one execution context, this is the case for most of the peripherals, like USART or I2C.

Other ones can be shared between several execution contexts, this is the case for system peripherals like PWR or RCC.

The legend below shows how assigned and shared peripherals are identified in the assignment diagram that follows.

Both the diagram below and the following summary table (in Internal peripherals runtime assignment and Internal peripherals boot time assignment chapters below) are clickable in order to jump to each peripheral overview article and get more detailed information (like the software frameworks used to control them). They list STMicroelectronics recommendations. The STM32MP13 reference manual [2] may expose more possibilities then what is shown here.

- Cortex-A7

- STGEN

- SYSCFG

- RTC

- EXTI

- GIC

- IWDG1

- IWDG2

- DMAMUX1

- DMAMUX2

- DMA1

- DMA2

- DMA3

- MDMA

- SAES

- ETZPC

- DDRMCE

- PKA

- TZC

- RNG

- HASH

- TAMP

- CRYP

- CRC

- SYSRAM

- DDR via DDRCTRL

- BKPSRAM

- SRAM1

- SRAM2

- SRAM3

- DCMIPP

- LTDC

- TIM

- LPTIM

- GPIO

- RCC

- PWR

- DTS

- DDRPERFM

- DBGMCU

- HDP

- BSEC

- QUADSPI

- FMC

- SDMMC

- USBH

- OTG

- USBPHYC

- USART

- I2C

- SPI

- FDCAN

- ETH

- VREFBUF

- DFSDM

- ADC

- SPI I2S

- SPDIFRX

- SAI

2. Internal peripherals runtime assignment[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| Analog | ADC | ADC1 | ☐ | ☐ | Assignment (single choice) |

| ADC2 | ☐ | ☐ | Assignment (single choice) ADC2 can be used for system supplies monitoring | ||

| Analog | DFSDM | DFSDM | ☐ | Assignment (single choice) | |

| Analog | VREFBUF | VREFBUF | ☐ | ☐ | Assignment (single choice) |

| Audio | SAI | SAI1 | ☐ | Assignment (single choice) | |

| SAI2 | ☐ | Assignment (single choice) | |||

| Audio | SPDIFRX | SPDIFRX | ☐ | Assignment (single choice) | |

| Core | RTC | RTC | ☑ | ☐ | RTC is mandatory to resynchronize STGEN after exiting low-power modes. |

| Core | STGEN | STGEN | ✓ | ||

| Core | SYSCFG | SYSCFG | ☑ | ☑ | |

| Core/DMA | DMA | DMA1 | ☐ | Assignment (single choice) | |

| DMA2 | ☐ | Assignment (single choice) | |||

| DMA3 | ⬚ | Assignment (single choice) | |||

| Core/DMA | DMAMUX | DMAMUX1 | ☐ | Assignment (single choice) | |

| DMAMUX2 | ⬚ | Assignment (single choice) | |||

| Core/DMA | MDMA | MDMA | ⬚ | ☐ | Shareable (multiple choices supported) |

| Core/Interrupts | EXTI | EXTI | ☐ | ☐ | |

| Core/Interrupts | GIC | GIC | ✓ | ✓ | |

| Core/IOs | GPIO | GPIOA-I | ☐ | ☐ | The pins can individually be secured |

| Core/RAM | BKPSRAM | BKPSRAM | ☑ | ⬚ | Assignment (single choice) |

| Core/RAM | DDRCTRL | DDR | ☑ | ⬚ | |

| Core/RAM | SRAM | SRAM1 | ☐ | ☐ | Assignment (between A7 S and A7 NS) |

| SRAM2 | ☐ | ☐ | Assignment (between A7 S and A7 NS) | ||

| SRAM3 | ☐ | ☐ | Assignment (between A7 S and A7 NS) | ||

| Core/RAM | SYSRAM | SYSRAM | ☑ | ☐ | Shareable (multiple choices supported)

Secure section required for low power entry and exit |

| Core/Timers | LPTIM | LPTIM1 | ☐ | ||

| LPTIM2 | ☐ | ☐ | Assignment (single choice) | ||

| LPTIM3 | ☐ | ☐ | Assignment (single choice) LPTIM3 can be used for HSE monitoring | ||

| LPTIM4 | ☐ | ||||

| LPTIM5 | ☐ | ||||

| Core/Timers | TIM | TIM1 (APB2 group) | ☐ | ||

| TIM2 (APB1 group) | ☐ | ||||

| TIM3 (APB1 group) | ☐ | ||||

| TIM4 (APB1 group) | ☐ | ||||

| TIM5 (APB1 group) | ☐ | ||||

| TIM6 (APB1 group) | ☐ | ||||

| TIM7 (APB1 group) | ☐ | ||||

| TIM8 (APB2 group) | ☐ | ||||

| TIM12 (APB6 group) | ☐ | ☐ | Assignment (single choice) TIM12 or TIM15 can be used for HSI/CSI calibration[3] | ||

| TIM13 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

| TIM14 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

| TIM15 (APB6 group) | ☐ | ☐ | Assignment (single choice) TIM12 or TIM15 can be used for HSI/CSI calibration[3] | ||

| TIM16 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

| TIM17 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

| Core/Watchdog | IWDG | IWDG1 | ☐ | ☐ | IWDG1 is secure programmable via ETZPC but this is not used / supported so not shown in STM32CubeMX |

| IWDG2 | ☐ | ☐ | Shared (none or both):

| ||

| High speed interface | OTG (USB OTG) | OTG (USB OTG) | ⬚ | ☐ | Assignment (single choice) |

| High speed interface | USBH (USB Host) | USBH (USB Host) | ☐ | ||

| High speed interface | USBPHYC (USB HS PHY controller) | USBPHYC (USB HS PHY controller) | ⬚ | ☐ | Assignment (single choice) |

| Low speed interface | I2C | I2C1 | ☐ | ||

| I2C2 | ☐ | ||||

| I2C3 | ☐ | ☐ | Assignment (single choice) | ||

| I2C4 | ☐ | ☐ | Assignment (single choice). Used for PMIC control on ST boards. | ||

| I2C5 | ☐ | ☐ | Assignment (single choice) | ||

| Low speed interface or audio |

SPI | SPI2S1 | ☐ | ||

| SPI2S2 | ☐ | ||||

| SPI2S3 | ☐ | ||||

| SPI2S4 | ⬚ | ☐ | Assignment (single choice) | ||

| SPI5 | ⬚ | ☐ | Assignment (single choice) | ||

| Low speed interface | USART | USART1 | ☐ | ☐ | Assignment (single choice) |

| USART2 | ☐ | ☐ | Assignment (single choice) | ||

| USART3 | ☐ | ||||

| UART4 | ☐ | ||||

| UART5 | ☐ | ||||

| USART6 | ☐ | ||||

| UART7 | ☐ | ||||

| UART8 | ☐ | ||||

| Mass storage | FMC | FMC | ⬚ | ☐ | Assignment (single choice) |

| Mass storage | QUADSPI | QUADSPI | ⬚ | ☐ | Assignment (single choice) |

| Mass storage | SDMMC | SDMMC1 | ⬚ | ☐ | Assignment (single choice) |

| SDMMC2 | ⬚ | ☐ | Assignment (single choice) | ||

| Networking | ETH | ETH1 | ⬚ | ☐ | Assignment (single choice) |

| ETH2 | ⬚ | ☐ | Assignment (single choice) | ||

| Networking | FDCAN | FDCAN1 | ☐ | ||

| FDCAN2 | ☐ | ||||

| Power & Thermal | DTS | DTS | ☐ | ||

| Power & Thermal | PWR | PWR | ✓ | ||

| Power & Thermal | RCC | RCC | ✓ | ✓ | |

| Security | BSEC | BSEC | ✓ | ☐ | |

| Security | CRC | CRC | ☐ | ||

| Security | CRYP | CRYP | ☐ | ☐ | Assignment (single choice) |

| Security | ETZPC | ETZPC | ✓ | ✓ | |

| Security | HASH | HASH | ☐ | ☐ | Assignment (single choice) |

| Security | DDRMCE | DDRMCE | ⬚ | ⬚ | |

| Security | PKA | PKA | ☐ | ⬚ | Assignment (single choice) |

| Security | RNG | RNG | ☐ | ☐ | Assignment (single choice) |

| Security | SAES | SAES | ☐ | ⬚ | Assignment (single choice) |

| Security | TAMP | TAMP | ☐ | ☐ | |

| Security | TZC | TZC | ✓ | ||

| Trace & Debug | DBGMCU | DBGMCU | ⬚ | ⬚ | |

| Trace & Debug | DDRPERFM | DDRPERFM | ☐ | ||

| Trace & Debug | HDP | HDP | ☐ | ||

| Visual | DCMIPP | DCMIPP | ☑ | ||

| Visual | LTDC | LTDC | ☐ | ☐ | Shareable (multiple choices supported) |

3. Internal peripherals boot time assignment[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 non-secure (U-Boot) | |||

| Analog | ADC | Any instance | ☐ | |||

| Analog | VREFBUF | VREFBUF | ☐ | |||

| Core | RTC | RTC | ☐ | |||

| Core | STGEN | STGEN | ✓ | ✓ | ||

| Core | SYSCFG | SYSCFG | ✓ | ☑ | ☑ | |

| Core/IOs | GPIO | GPIOA-I | ✓ | ☑ | ☐ | The pins can individually be secured |

| Core/RAM | BKPSRAM | BKPSRAM | ☑ | ⬚ | ||

| Core/RAM | DDRCTRL | DDR | ☑ | ⬚ | ||

| Core/RAM | SRAM | Any instance | ✓ | ☑ | ☐ | SRAM first used by ROM code, then TF-A BL2. After assignment free to user |

| Core/RAM | SYSRAM | SYSRAM | ✓ | ✓ | ||

| Core/Timers | LPTIM | LPTIM1 | ⬚ | |||

| LPTIM2 | ⬚ | ⬚ | ||||

| LPTIM3 | ⬚ | ⬚ | ||||

| LPTIM4 | ⬚ | |||||

| LPTIM5 | ⬚ | |||||

| Core/Timers | TIM | TIMx (x = 1 to 8, APB2 group) |

⬚ | |||

| TIMx (x = 2 to 7, APB1 group) |

⬚ | |||||

| TIMx (x = 12 to 17, APB6 group) |

⬚ | ⬚ | ||||

| Core/Watchdog | IWDG | Any instance | ✓ | ☐ | ☐ | |

| High speed interface | OTG (USB OTG) | OTG (USB OTG) | ✓ | ☐ | ☐ | The OTG can be used by ROM code, FSBL and SSBL in DFU mode to support serial boot. It can be used also in U-boot with command line tools. |

| High speed interface | USBH (USB Host) | USBH (USB Host) | ☐ | |||

| High speed interface | USBPHYC (USB HS PHY controller) | USBPHYC (USB HS PHY controller) | ✓ | ☐ | ☐ | The USBPHYC can be used by ROM code, FSBL and SSBL in DFU mode to support serial boot. It can be used also in U-boot by OTG and USBH with command line tools. |

| Low speed interface | I2C | Any instance | ☐ | ☐ | ||

| Low speed interface | USART | Any instance | ✓ | ☐ | ☐ | |

| Mass storage | FMC | FMC | ☐ | ☐ | ☐ | |

| Mass storage | QUADSPI | QUADSPI | ✓ | ☐ | ☐ | |

| Mass storage | SDMMC | SDMMC1 | ☐ | ☐ | ☐ | |

| SDMMC2 | ☐ | ☐ | ☐ | |||

| Networking | ETH | Any instance | ☐ | Assignment (single choice) | ||

| Power & Thermal | PWR | PWR | ✓ | ✓ | ||

| Power & Thermal | RCC | RCC | ✓ | ✓ | ✓ | |

| Security | BSEC | BSEC | ✓ | ✓ | ☐ | |

| Security | CRYP | CRYP | ☑ | ⬚ | ⬚ | ROM code allocation is managed with the bit 7 in OTP 9 |

| Security | ETZPC | Any instance | ✓ | ✓ | ✓ | ETZPC configuration is set by OP-TEE |

| Security | HASH | HASH | ✓ | ☑ | ||

| Security | DDRMCE | DDRMCE | ☑ | |||

| Security | PKA | PKA | ✓ | ☑ | ⬚ | Assignment is mandatory only for secure boot |

| Security | RNG | RNG | ✓ | ☑ | ☐ | Required for DPA peripheral protection |

| Security | SAES | SAES | ☐ | ☑ | ROM code allocation is managed with the bit 7 in OTP 9 | |

| Security | TAMP | TAMP | ✓ | ✓ | ✓ | |

| Security | TZC | TZC | ☑ | |||

| Trace & Debug | DBGMCU | DBGMCU | ⬚ | ⬚ | ⬚ | |

| Visual | LTDC | LTDC | ☐ | |||

4. References[edit | edit source]