If you are looking for a cost effective and power efficient microprocessor with a state of the art Linux distribution, the STM32MP21 may be your solution!

Still want an heterogeneous architecture, like the other STM32MP2 Series microprocessors? No problem, the STM32MP21 embeds an Arm® Cortex®-A35 and an Arm® Cortex®-M33.

And, if you want to scale up to the STM32MP23 and STM32MP25, we deliver the STM32MP21 in the same 10x10 package that is pin compatible with the rest of the family.

This article introduces the STM32MP21x lines ![]() , and gives information about the part number codification and block diagram. Then technical aspects are introduced, providing information on:

, and gives information about the part number codification and block diagram. Then technical aspects are introduced, providing information on:

- STM32MP21 documentation,

- articles dedicated to internal peripherals that make the transition towards the software frameworks required to control these peripherals,

- the board supporting STM32MP21 microprocessors,

- the supported software distributions, that can be downloaded into the STM32MP21 microprocessors.

1. Introduction[edit | edit source]

STM32MP21 microprocessors are targeting industry 4.0, human-machine interfaces (up to 1080p60), and a wide range of smart products that require a very high level of security, such as IoT and payment applications.

STM32MP21 microprocessors are based on a heterogenous architecture embedding an Arm® Cortex®-A35 core and an Arm® Cortex®-M33 coprocessor, both supporting Arm®Trustzone® mode for secure operations.

On top of this, it relies on the connectivity foundations from the STM32MP2 series with dual Gigabit ETH (with TSN end-point support), that enlarge the possibilities in industrial, smart city and smart home applications.

The STM2MP21 also comes with a resource isolation framework (RIF) that is a very flexible and powerful infrastructure allowing to decide which Arm® Cortex® will boot first and to associate each peripheral to a hardware execution context or traffic initiator (like a DMA).

2. Part number codification[edit | edit source]

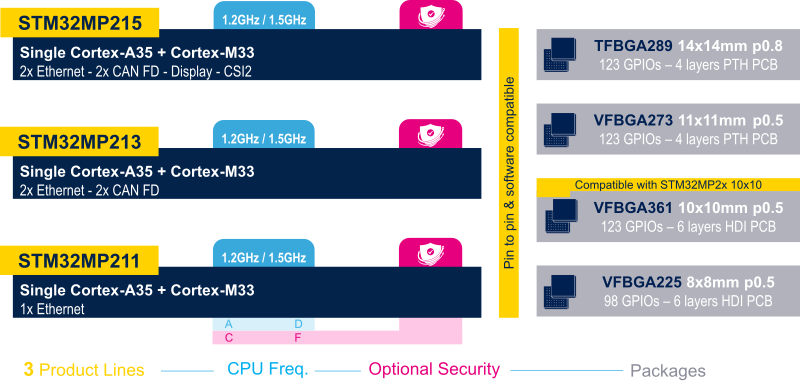

The figure below shows the differences between the three STM32MP21x lines, with their security and frequency options. Each line can be delivered in one of four packages represented on the right side: refer to the technical documentation to get details on the available features per package.

The tables below explains how the part numbers are encoded for all the above combinations.

2.1. STM32MP21x lines[edit | edit source]

Cortex-A35 Cortex-M33 Display Camera FDCAN Gigabit Ethernet interfaces STM32MP215 Single Yes Yes Parallel and MIPI CSI-2 2 2 STM32MP213 Single Yes No Parallel 2 2 STM32MP211 Single Yes No Parallel No 1

2.2. Security and Arm Cortex-A35 frequency[edit | edit source]

Security Cortex-A35 frequency STM32MP21xA Basic 1200 MHz[1] STM32MP21xC Secure boot + Cryptography 1200 MHz[1] STM32MP21xD Basic 1500 MHz[1] STM32MP21xF Secure boot + Cryptography 1500 MHz[1]

2.3. Packages[edit | edit source]

STM32MP21xxAM TFBGA289, 14x14mm, pitch 0.8mm 123 GPIOs STM32MP21xxAN VFBGA273, 11x11mm, pitch 0.5mm 123 GPIOs STM32MP21xxAL VFBGA361, 10x10mm, pitch 0.5mm 123 GPIOs STM32MP21xxAO VFBGA225, 8x8mm, pitch 0.5mm 98 GPIOs

2.4. Junction temperature[edit | edit source]

STM32MP21xxxx3 - 40 to + 125 °C

3. Block diagram[edit | edit source]

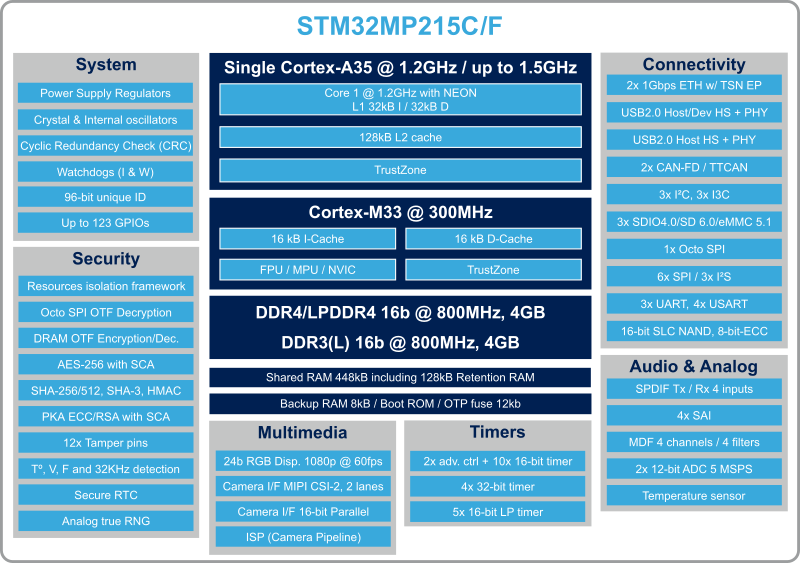

Here below is the STM32MP215F block diagram offering the richest features set of the STM32MP21 microprocessor.

The above figure shows a functional view of the design that does not aim to be aligned with the real design: it shows the available features and not how they are implemented into the microprocessor.

4. Technical documentation[edit | edit source]

- STM32MP21 reference manuals: device and internal peripheral user specifications

- STM32MP21 datasheets: electrical characteristics, package, and pinout descriptions

5. Internal peripherals[edit | edit source]

STM32MP21 peripherals overview article gives a description of all the internal peripherals available on STM32MP21 devices, with direct links to the articles where you can find:

- an overview of each peripheral,

- the list of instances available for each peripheral type,

- information on the way each instance can be shared between Arm® Cortex®-A35 and Cortex®-M33 cores,

- direct links to the software frameworks used to control the peripheral from different Arm® cores and security modes such as Cortex®-A35 non secure, Cortex®-A35 secure, Cortex®-M33 non secure, or Cortex®-M33 secure.

6. How to get further with STM32MP21 ecosystem[edit | edit source]

6.1. Boards[edit | edit source]

| In a first time, the STM32MP21 Discovery kit description and the boards are reserved to the early adopters, so contact your local sales if you want to be part of the Alpha program and discover this new ST platform. |

6.2. Supported software distributions[edit | edit source]

| In a first time, the STM32MP21 software distributions and the complete ecosystem (including documentation and tools) are reserved to the early adopters, so contact your local sales if you want to be part of the Alpha program and start to play with the new STM32MP21x ecosystem release. |