1. Article purpose[edit | edit source]

This article explains the STM32MP1 Series DMA topology and the associated configurations recommended by ST.

2. DMA specificities per STM32 MPU devices[edit | edit source]

2.1. STM32MP13x lines  [edit | edit source]

[edit | edit source]

The STM32MP13xx MPUs feature four DMA instances:

- 1 MDMA internal peripheral dedicated to the transfers between some internal peripherals and the external memories (DDR), and between the internal and external memories.

- 3 DMA internal peripheral (DMA1/DMA2/DMA3) dedicated to the transfers between internal peripherals and the internal SRAM. The DMA1 and DMA2 instances are coupled with DMAMUX1. DMA3 is coupled with DMAMUX2: DMAMUX internal peripheral is in charge of routing the internal peripheral requests to the DMA channels.

2.2. STM32MP15x lines  [edit | edit source]

[edit | edit source]

The STM32MP15xx MPUs feature three DMA instances:

- 1 MDMA internal peripheral dedicated to the transfers between some internal peripherals and the external memories (DDR), and between the internal and external memories.

- 2 DMA internal peripheral (DMA1/DMA2) dedicated to the transfers between internal peripherals and the internal SRAM. These two DMA instances are coupled with a DMAMUX internal peripheral in charge of routing the internal peripheral requests to the DMA channels.

3. DMA configurations[edit | edit source]

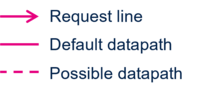

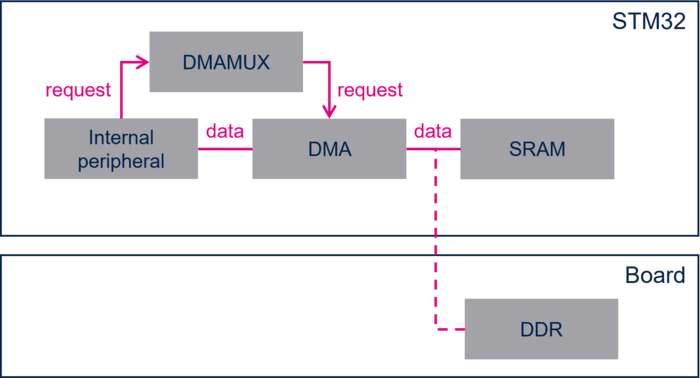

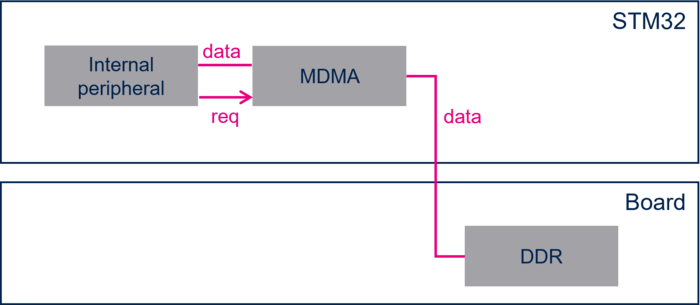

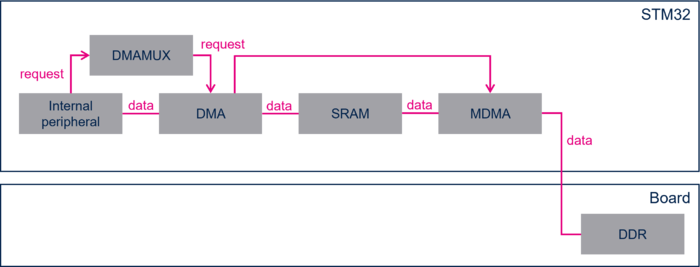

The following figures show the different DMA configurations available on STM32MP1 and the associated requests and data connections. The legend below illustrates the request lines and datapath.

- Internal peripherals - internal SRAM with DMA transfer

- In this configuration, the dataflow is:

- Internal peripherals - DDR with MDMA transfer

- In this configuration, the dataflow is:

- In this configuration, the dataflow is:

- peripheral to memory direction: data are transferred from the peripheral to the temporary internal SRAM buffer by DMA, then from the temporary internal SRAM buffer to the DDR buffer by MDMA.

- memory to peripheral direction: data are transferred from the DDR buffer to the temporary internal SRAM buffer by MDMA, then from the temporary internal SRAM buffer to the peripheral by DMA.

For more information about the DMA controllers above, and to know the DMA configuration that must be used with each internal peripheral, refer to reference manuals corresponding to the used STM32 MPU .

4. STMicroelectronics recommendations[edit | edit source]

4.1. For Arm® Cortex®-M4 execution context[edit | edit source]

The Arm® Cortex®-M4 accesses by default the internal SRAM for code and data.

In this context, the DMA transfers operate only between the peripheral and the internal SRAM.

This is why ST recommends to dedicate one DMA internal peripheral to Arm® Cortex®-M4.

4.2. For Arm® Cortex®-A7 secure execution context[edit | edit source]

The Arm® Cortex®-A7 secure firmware is located in SYSRAM (both code and data). As the internal peripherals and the SYSRAM associated to the Arm® Cortex®-A7 secure context are also secure, the MDMA must be used to support transfers between them because it is secure aware.

4.3. Arm® Cortex®-A7 nonecure execution context[edit | edit source]

The Arm® Cortex®-A7 nonsecure firmware is mainly located in the external memory (DDR). In consequence, the DMA transfers operate between the peripherals and the DDR. Nevertheless, as the different internal peripherals do not have the same requirements in term of bandwidth, real time, and flow control, the user must use one of the three DMA configurations described in DMA configurations. To make the selection easier, the following table sums up the possible choices for each peripheral and highlights the recommended configuration. Note that this configuration is set by default in the device tree (dtsi).

| Peripheral | no DMA mode | DMA mode | MDMA mode | DMA-MDMA chaining mode | Default mode |

|---|---|---|---|---|---|

| U(S)ART | no DMA mode | ||||

| ADC | DMA-MDMA chaining mode | ||||

| SPI | DMA or MDMA mode depending on instance | ||||

| SPDIFRx | DMA mode | ||||

| SAI | DMA mode | ||||

| I2C | DMA or MDMA mode depending on instance | ||||

| Timer | DMA-MDMA chaining mode | ||||

| DFSDM | DMA mode | ||||

| I2S | DMA mode | ||||

| DCMI | DMA-MDMA chaining mode | ||||

| FMC | MDMA mode | ||||

| QUADSPI | MDMA mode | ||||

| HASH | MDMA mode | ||||

| CRYP | MDMA mode |

5. STMicroelectronics reference boards default configuration[edit | edit source]

5.1. STM32MP135x-DK Discovery kit  DMA configuration[edit | edit source]

DMA configuration[edit | edit source]

The following table provides the list of the peripherals for which DMA is configured. Associated configurations are also described.

| Peripheral | Request line | DMA mode |

|---|---|---|

| ADC1 | rx | DMA-MDMA chaining mode |

| ADC2 | rx | DMA-MDMA chaining mode |

| CRYP1 | in | MDMA mode |

| out | ||

| HASH1 | in | MDMA mode |

| I2S2 | rx | DMA mode |

| tx | ||

| SAI2 | a - tx | DMA mode |

| b - rx | ||

| USART2 | rx | DMA mode |

| tx |

5.2. STM32MP157x-EV1 Evaluation board  DMA configuration[edit | edit source]

DMA configuration[edit | edit source]

The following table provides the list of the peripherals for which DMA is configured. Associated configurations are also described.

| Peripheral | Request line | DMA mode |

|---|---|---|

| CRYP1 | in | MDMA mode |

| out | ||

| DCMI | tx | DMA-MDMA chaining mode |

| DFSDM | channel 0 - rx | DMA mode |

| channel 1 - rx | ||

| channel 2 - rx | ||

| channel 3 - rx | ||

| HASH1 | in | MDMA mode |

| I2S2 | rx | DMA mode |

| tx | ||

| SAI2 | a - tx | DMA mode |

| b - rx | ||

| USART2 | rx | DMA mode |

| tx |

5.3. STM32MP157x-DK2 Discovery kit  DMA configuration[edit | edit source]

DMA configuration[edit | edit source]

The following table provides the list of the peripherals for which DMA is configured. Associated configurations are also described.

| Peripheral | Request line | DMA mode |

|---|---|---|

| CRYP1 | in | MDMA mode |

| out | ||

| HASH1 | in | MDMA mode |

| I2S2 | rx | DMA mode |

| tx | ||

| SAI2 | a - tx | DMA mode |

| b - rx | ||

| USART2 | rx | DMA mode |

| tx |