1. Article purpose[edit | edit source]

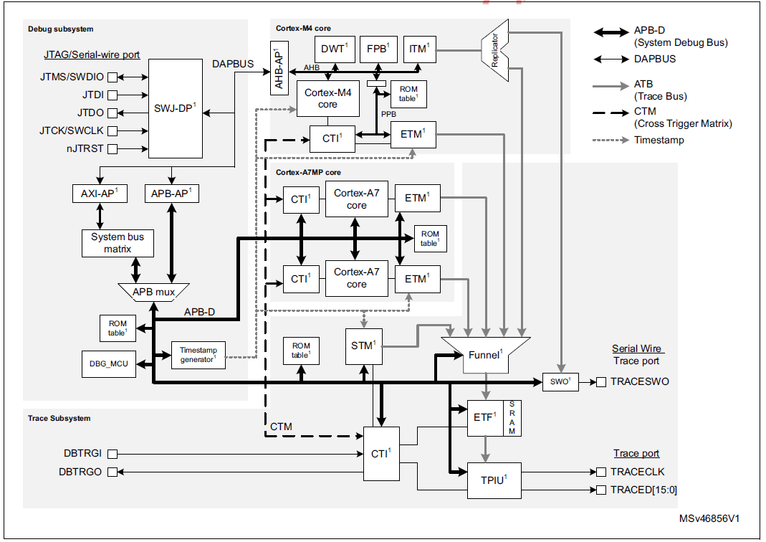

The purpose of this article is to provide information on the Arm® CoreSight™ hardware subsystem.

It explains what are the principle peripherals of this subsystem.

2. Peripheral overview[edit | edit source]

Arm® CoreSight™ products include

- a wide range of trace macrocells for Arm® processors,

To enable the debug and trace of the most complex, multi-core SoCs, Arm® CoreSight™ products include

- a system and software instrumentation,

- and a comprehensive set of IP blocks.

Arm® has defined an open CoreSight architecture to allow SoC designers to add "debug and trace" capabilities for other IP cores in to the CoreSight™ infrastructure.

2.1. Components description[edit | edit source]

The debug features are based on Arm® CoreSight™ components

| Arm® CoreSight™ components | STM32MP13x lines |

STM32MP15x lines |

|---|---|---|

| SWJ-DP: JTAG/Serial-wire debug port | ||

| AXI-AP: AXI access port | ||

| AHB-AP: AHB access port | ||

| APB-AP: APB access port | ||

| ITM: Instrumentation Trace Macrocell | ||

| DWT: Data Watchpoint and Trace | ||

| FPB: Flash Patch and Breakpoint | ||

| ETM: Embedded Trace Macrocell | ||

| ETF: Embedded Trace FIFO | ||

| TPIU: Trace Port Interface Unit | ||

| SWO: Serial Wire Output | ||

| CTI: Cross Trigger Interface | ||

| CTM: Cross Trigger Matrix | ||

| TSGEN: Timestamp Generator | ||

| STM: System Trace Macrocell |

More information about these components can be found in the Arm® website [1]

2.2. Features[edit | edit source]

Refer to the Debug support (DBG) chapter of reference manuals corresponding to the STM32 MPU, you use, for the complete list of features, and to the software components, introduced above, to see which features are really implemented.

3. References[edit | edit source]