The purpose of this article is to describe the basic steps required to tune or troubleshoot the USB High-Speed PHYs from hardware and software perspectives.

1. General recommendations[edit source]

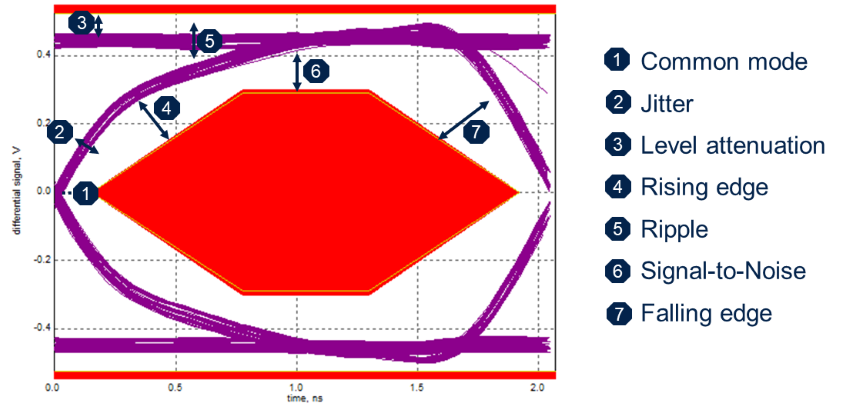

The eye diagram is characterized with a specific reference resistor on board, between the STM32 MPU device USB_RREF pin and ground.

Verify first that USB_RREF resistor is correctly connected and has proper value and precision (3 kΩ 1%)

2. Eye Diagram[edit source]

2.1. Common mode troubleshooting[edit source]

- Hardware root causes to investigate

- Mismatch between D+ and D- (in terms of length and/or parallelism)

- Check layout and add common mode filter (e.g. ECMF02-2AMX6[1])

2.2. Jitter troubleshooting[edit source]

- Hardware root causes to investigate

- Too much capacitance (component or PCB) on D+/D- lines

- USB Power/GND instability

- Check decoupling / Check grounding

- Fine tuning may be performed by using USBPHYC device tree configuration [2]

High jitter has an HW root cause in most cases.

- USBPHYC_TUNEx.HSDRVRFRED

- 0: increase rising edge but add jitter (i.e. remove st,enable-hs-rftime-reduction;[3])

- USBPHYC_TUNEx.INCURREN/.INCURRINT

- Tune current increase with .INCURREN or .INCURRINT (i.e. remove st,current-boost-microamp= <n>;[3] or set it to 1000µA or 2000µA)

- USBPHYC_TUNEx.HSDRVCHKITRM

- Reduce the increase of the main level (i.e. reduce value of st,trim-hs-current = <n>;[3])

2.3. Level attenuation or Signal-to-Noise troubleshooting[edit source]

- Hardware root causes to investigate

- too much serial resistance and capacitance (component or PCB) on D+/D- lines

- USB Power/GND instability

- Check decoupling / Check grounding

- Software potential tuning

- USBPHYC_TUNEx.HSDRVCHKITRM

- Higher the value, higher will be the level of signal (i.e. increase value of st,trim-hs-current = <n>;[3]).

- But noise and ripple can appear

- USBPHYC_TUNEx.HSDRVCURINCR/.HSDRVDCLEV

- Higher the value, higher will be the margin for the level (i.e. increase value of st,hs-dc-level = <n>;[3]).

- But jitter in the rising edge and noise can appear

2.4. Rising edge or Falling edge troubleshooting[edit source]

- Hardware root causes to investigate

- too much serial resistance and capacitance (component or PCB) on D+/D- lines

- Impedance mismatch : check characteristic impedance of lines, stubs…

- Software potential tuning

- USBPHYC_TUNEx.HSDRVRFRED

- 0: improve rising edge (i.e. remove st,enable-hs-rftime-reduction;[3])

- 1: slow-down rising edge (i.e. add st,enable-hs-rftime-reduction;)

- Potential impact on jitter

- USBPHYC_TUNEx.HSDRVCHKITRM

- Depending on level, slope is increased/decreased (i.e. adjust value of st,trim-hs-current = <n>;[3])

- USBPHYC_TUNEx.HSDRVSLEW

- 0: normal rising edge (i.e. remove st,decrease-hs-slew-rate;[3])

- 1: reduce rising edge (i.e. add st,decrease-hs-slew-rate;)

- Useful to reduce a hill shape ripple on top of rising/falling edge

- USBPHYC_TUNEx.HSDRVCURINCR/.HSDRVDCLEV

- Improve slope speed (i.e. increase value of st,hs-dc-level = <n>;[3]).

- But jitter in the rising edge and noise can appear

2.5. Ripple troubleshooting[edit source]

- Hardware root causes to investigate

- Impedance mismatch : check characteristic impedance of lines, stubs…

- Software potential tuning

- USBPHYC_TUNEx.HSDRVCHKZTRM[1:0]

- 00: Usually open the eye but can create some jitter and ripple (i.e. st,trim-hs-impedance = <0>;[3])

- 11: Close the eye but can reduce jitter and ripple (i.e. st,trim-hs-impedance = <3>;)

- USBPHYC_TUNEx.HSDRVSLEW

- 0: normal rising edge (i.e. remove st,decrease-hs-slew-rate;[3])

- 1: reduce rising edge (i.e. add st,decrease-hs-slew-rate;)

- Useful to reduce a hill shape ripple on top of rising/falling edge

3. Link between Register values and Device Tree description[edit source]

Only few bitfields should be adjusted in the scope of Eye Diagram tuning. It is recommended to keep other as described in default Device Tree examples. See also USBPHYC device tree bindings[3]

| Device Tree item | details | USBPHYC_TUNEx field |

|---|---|---|

| st,current-boost-microamp | <1000> current boosting of 1mA | .INCURREN=1/.INCURRINT=0 |

| <2000> current boosting of 2mA | .INCURREN=1/.INCURRINT=1 | |

| st,no-lsfs-fb-cap | disables the LS/FS feedback capacitor | .LFSCAPEN=1 |

| st,decrease-hs-slew-rate | slows the HS driver slew rate by 10% | .HSDRVSLEW=1 |

| st,hs-dc-level | <0> normal level | .HSDRVCURINCR=0/.HSDRVDCCUR=0 |

| <1> increases the HS driver DC level by 5 to 7mV | .HSDRVCURINCR=1/.HSDRVDCLEV=0 | |

| <2> increases the HS driver DC level by 10 to 14mV | .HSDRVCURINCR=1/.HSDRVDCLEV=1 | |

| <3> decreases the HS driver DC level by 5 to 7mV | .HSDRVDCCUR=1 | |

| st,enable-fs-rftime-tuning | enables the FS rise/fall tuning option | .FSDRVRFADJ=1 |

| st,enable-hs-rftime-reduction | enables the HS rise/fall reduction feature | .HSDRVRFRED=1 |

| st,trim-hs-current | controls HS driver current trimming for choke | .HSDRVCHKITRM=n [0:15] |

| st,trim-hs-impedance | controls HS driver impedance tuning for choke | .HSDRVCHKZTRM=n [0:3] |

| st,tune-squelch-level | adjusts the squelch DC threshold value | .SQLCHCTL=n [0:3] |

| st,enable-hs-rx-gain-eq | enables the HS Rx gain equalizer | .HDRXGNEQEN |

| st,tune-hs-rx-offset | adjusts the HS Rx offset | .HSRXOFF=n [0:3] |

| st,no-hs-ftime-ctrl | disables the HS fall time control of single ended signals during pre-emphasis | .HSFALLPREEM=1 |

| st,no-lsfs-sc | disables the short circuit protection in LS/FS driver | .SHTCCTCTLPROT |

| st,enable-hs-tx-staggering | enables the basic staggering in HS Tx mode | .STAGSEL |

4. Software configuration to enter test modes[edit source]

This section describes how to

4.1. Device tree configuration[edit source]

The Target Peripheral List (TPL) is used to identify targeted devices during Embedded Host compliance testing. The user can add "tpl-support" in the board device tree file to enable it.

# Enable Target Peripheral List on USBH, on both EHCI and OHCI controllers: &usbh_ehci { + tpl-support; }; &usbh_ohci { + tpl-support; };

# Enable Target Peripheral List on OTG: &usbotg_hs { + tpl-support; };