1. Article purpose[edit source]

The purpose of this article is to give information about the Arm® CoreSight™ hardware subsystem.

It explains what are the principle peripherals of this subsystem.

2. Peripheral overview[edit source]

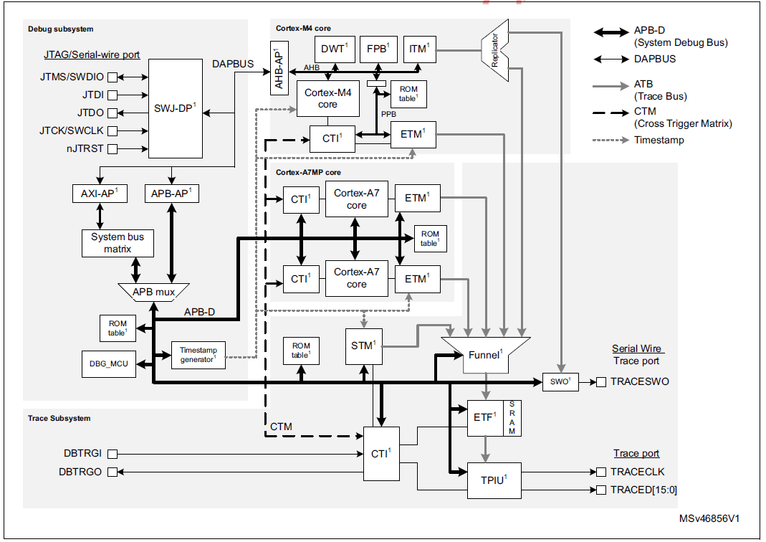

Arm® CoreSight™ products include a wide range of trace macrocells for Arm® processors, system and software instrumentation and a comprehensive set of IP blocks to enable the debug & trace of the most complex, multi-core SoCs.

Arm® has defined an open CoreSight architecture to allow SoC designers to add debug & trace capabilities for other IP cores in to the CoreSight infrastructure.

2.1. Components description[edit source]

The debug features are based on Arm® CoreSight™ components:

• SWJ-DP: JTAG/Serial-wire debug port

• AXI-AP: AXI access port

• AHB-AP: AHB access port (not available on STM32MP13x lines ![]() )

)

• APB-AP: APB access port

• ITM: Instrumentation Trace Macrocell

• DWT: Data Watchpoint and Trace

• ETM: Embedded Trace Macrocell

• ETF: Embedded Trace FIFO

• TPIU: Trace Port Interface Unit

• SWO: Serial Wire Output (not available on STM32MP13x lines ![]() )

)

• CTI: Cross Trigger Interface

• CTM: Cross Trigger Matrix

• TSGEN: Timestamp Generator

• STM: System Trace Macrocell (not available on STM32MP13x lines ![]() )

)

More information about these components can be found in the Arm® website [1]

2.2. Features[edit source]

For the complete list of features, and to the software components, introduced below, to see which features are really implemented, refer to:

- the STM32MP13 reference manuals STM32MP13x lines

- the STM32MP15 reference manuals STM32MP15x lines

3. References[edit source]