1. Article purpose[edit source]

This article introduces STM32CubeMP25 Package / STM32CubeMP2 Package (a.k.a., STM32CubeMP25 / STM32CubeMP2) architecture based on the Arm® Cortex®-M33 processor, acting as coprocessor of the Arm® Cortex®-35.

- Refer to STM32CubeMP25 Package - Getting started article to get started.

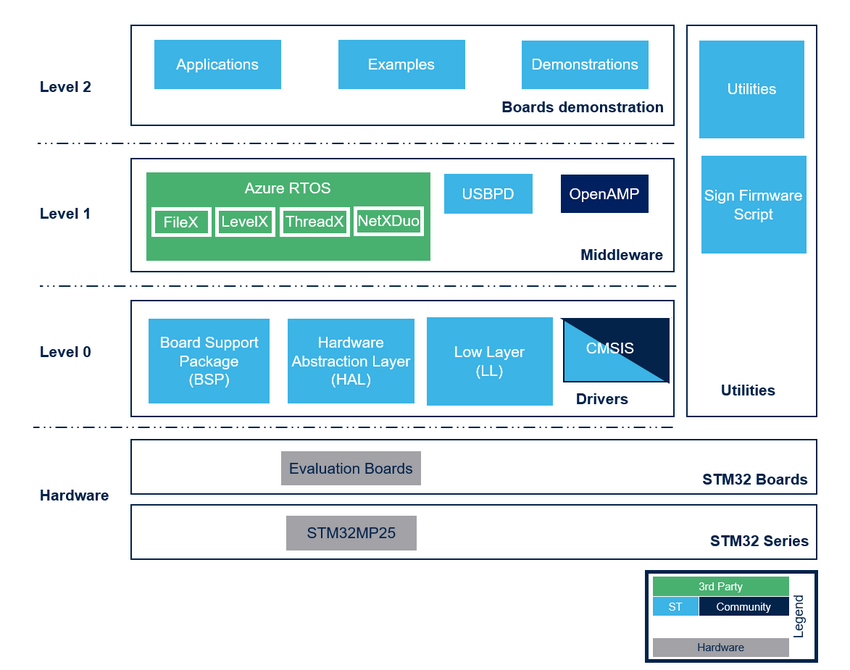

2. Architecture overview[edit source]

The STM32CubeMP25 Package gathers together, in a single package, all the generic embedded software components required to develop applications on top of Arm® Cortex®-M33 microprocessors.

On top of the hardware, the STM32CubeMP25 Package solution is built around three levels of software components (Level 0 for Drivers, level 1 for Middleware. Level 2 for Boards demonstrations), that interact easily with each other. It also includes 2 common components CMSIS and Utilities which interact with all two levels.