1. Introduction

The STM32CubeWBA firmware provides low-power features that are integrated into the application framework.

Once the low power is enabled in the application, the system framework is responsible of choosing the lowest possible power mode that can be used. Several parameters are taken into account such as the application use case or the radio activity.

2. Concepts

2.1. Low-power general overview

STM32WBA SoC low-power mode is determined by both Link Layer operating modes and SoC PWR modes.

Details are given in the next sections.

2.1.1. Link Layer operating modes

Link Layer operating modes are detailed in the table below.

| Operating mode | Purpose |

|---|---|

| Active – Standby* | Link Layer is in active mode when the radio is operating. Standby is used on active waiting of radio event (Bluetooth® Low Energy IFS, Rx on IDLE for 802.15.4). |

| Sleep | This mode is used when there is no radio activity. Baseband clock (active clock) has to be switched OFF. RXTX SRAM or sequence SRAM are not available. Hardware Link Layer registers are accessible as long as bus clock remains ON. |

| Deep-sleep | Deep-sleep mode is the lowest low-power mode for Link Layer IP. This mode is only available when the is no current/up-coming radio activity. Baseband clock (active clock) is switched OFF. All power domains are switched OFF except sleep timer one. The bus clock has to be ON for sleep timer registers access. |

* Note: The Link Layer 'Standby' mode is unrelated to the STM32WBA SoC Standby mode!

Deep-sleep mode entry/exit is time consuming. Therefore, the next radio activity has to be far enough to power down the radio.

A threshold value is available in the system framework and can be configured as needed. See RADIO_DEEPSLEEP_WAKEUP_TIME_US macro in system configuration.

2.1.2. SoC PWR power modes

STM32WBA SoC supports four main PWR power modes: RUN, SLEEP, STOP0/1 and STANDBY:

2.1.2.1. Run mode

The CPU and the system clock are running. It shall be used only when it is required to execute code.

2.1.2.2. Sleep mode

CPU clock is off (CPU stops fetching code), all peripherals including a Cortex®-M33 core such as NVIC and SysTick can run and wake up the CPU when an interrupt or an event occurs. This should be used when a peripheral (that does not have a kernel clock) requires the system clock to operate while the CPU is stopped.

2.1.2.3. Stop modes

Stop modes achieve the lowest power consumption while retaining the content of registers. The SRAM content can be selected to be retained or not. All clocks (except some autonomous peripherals bus and kernel clocks) in the Core domain are stopped (system clock, high-speed oscillators).

There are two stop modes:

- STOP0: Used when the kernel clock or bus clock is required by an autonomous peripheral.

The 2.4GHz radio can still be active when in Stop 0 Range 1. For this, the high-speed system clock and peripheral kernel clocks may be kept running. - STOP1: Lowest Stop mode available in WBA5x series where all bus and kernel clocks are off.

2.1.2.4. Standby modes

The Standby mode is used to achieve the lowest power consumption. The internal regulator is switched off (Core domain is powered off). All high-speed clock sources are shut off (PLL, HSE, and HSI). The LSE or LSI can still run.

When entering Standby mode, register contents are lost except for registers in the backup domain and standby circuitry. Regarding peripherals, only RTC, TAMP, and WKUP are retained. Standby mode exit leads to a SoC reset.

The Standby mode described above is Standby without retention.

Optionally, the user can retain the content of SRAMs. This is called Standby with retention mode.

- The full SRAM1 and/or SRAM2 can be retained in Standby mode, supplied by the low-power regulator.

- The 2.4 GHz RADIO Sleep Timer, RXTXRAM, and sequence SRAM can be retained in Standby mode, supplied by the low-power regulator.

2.2. Low-power in Connectivity applications

2.2.1. Low-power manager Utility (LPM)

2.2.1.1. LPM Utility

The low-power manager provides a simple interface to receive the input from up to 32 different users and computes the lowest possible power mode the system can use. Each LPM client can request a disablement (or reenablement after deactivation) for Stop and Standby modes when necessary. The API to use is:

UTIL_LPM_SetStopModefor Stop mode.UTIL_LPM_SetOffModefor Standby mode.

Low power Sleep mode is selected when Stop and Standby modes are disabled.

Users can obtain the Low-power mode that is going to be selected at that time with UTIL_LPM_GetMode API.

2.2.1.2. Platform interfaces

Once it is time to enter in Low-power mode, the application is responsible to call UTIL_LPM_EnterLowPower. According to the lowest Low-power mode available, LPM Utility calls the appropriate interface to enter Sleep, Stop, or Standby mode at SoC level. Those interfaces have to be defined at application level (system side).

Low power platform interfaces are:

PWR_EnterSleepModeandPWR_ExitSleepModefor Sleep mode.PWR_EnterStopModeandPWR_ExitStopModefor Stop mode.PWR_EnterOffModeandPWR_ExitOffModefor Standby mode.

2.2.2. Low-power Stop modes for Connectivity

Both STOP0 and STOP1 are supported. As a reminder:

- When Link Layer is in active/standby mode, SoC can achieve STOP0.

- When the Link Layer is in sleep mode, SoC can achieve STOP1.

2.2.2.1. Low-power Stop mode entry

Section for Standby mode entry added with the same explanation. The function Enter_Stop_Standby_Mode is used to factorize the code as the first steps for Stop mode entry are the same as Standby. Not mentioned in the wiki as it can be confusing for the end-user.

This is mandatory because it is the only way for entering Stop mode.}} Below is the mandatory system configuration before entering Stop modes (in order)

- ICache IP shall be disabled.

- Flash latency: 3, SRAM1/2 latencies: 1.

- CPU shall be in deep-sleep mode.

- PWR VOS shall be stable.

2.2.2.2. Low-power Stop mode exit

At Low-power Stop mode exit, the system clock manager (SCM) module may be called to reconfigure the system clock as it was before entering low power.

See System Clock Manager for further information about this system module.

2.2.3. Low-power Standby mode for connectivity

2.2.3.1. Standby mode entry

Below is the mandatory system configuration before entering Standby mode (in order)

- ICache IP shall be disabled.

- Flash latency: 3, SRAM1/2 latencies: 1.

- CPU shall be in deep sleep mode.

- PWR VOS shall be stable.

2.2.3.2. Standby strategy

For connectivity applications with RF activity, the lowest power mode achievable is Standby with retention. The system must retain:

- Link Layer configuration and context: Link Layer dedicated SRAM retained.

- Application content: at least SRAM1 retained. If SRAM1 is not enough RAM for the application, SRAM2 must also be retained.

As the CPU is reset when exiting the standby mode, nonretained configuration (SRAMs content) must be reapplied (e.g SoC register content). This concerns:

- NVIC interrupts, system, and user/application related.

For the system side, Link Layer high priority, Link Layer software low priority, RCC, RTC interrupts are configured (priority) and reenabled. - Link Layer peripheral clock (radio bus clock) is reenabled.

- SoC IPs are reinitialized completely (including related NVIC interrupts if handled by HAL software).

- RTC peripheral clock. RTC registers are retained (RTC IP is part of the backup domain), however the RTC peripheral clock must be reinitialized.

2.2.3.3. Save & restore mechanism

2.2.3.3.1. CPU context registers

Default behavior at standby exit - after CPU reset - is to execute Reset handler code. For connectivity applications, the goal is to execute the low-power standby exit procedure (PWR_ExitOffMode function after __WFI) as the system does for Stop mode.

Hereafter is the description of the mechanism for the WBA5 solution.

- At Standby entry, the system saves the CPU registers related to the execution context. This concerns:

- Stack pointers related registers (PSP, PSPLIM, MSPLIM), saved in retained variables.

- OS related interruption priorities (SysTick, SVCall, and PendSV), saved in retained variables.

- R4-R12, LR, and SP (MSP) general purpose registers that are backup in the CPU stack (by calling

CPUcontextSave).

- Connectivity applications have a specific Reset handler (the default reset handler is overridden) that restores CPU context registers from the CPU stack if the system resets from standby exit.

- As a result, the next executed instruction is the one after

__WFIinPWR_EnterOffMode.

2.2.3.3.2. CPU peripherals registers

CPU peripheral registers are also maintained with backup_system_register and restore_system_register APIs.

Connectivity system register data that is preserved include:

- SCB

CPACR(FPU related). - SysTick

CTRL/LOAD/VAL.

2.2.3.4. Standby dynamic view

Here is the steps that the system performs to manage Standby mode (when application is IDLE):

- Link Layer deep-sleep entry

If there is enough time before the next radio event:

- Link Layer IP internal timer is programmed to wake up before the next radio event with configurable threshold.

- Link Layer is switched to the deep-sleep mode.

- Standby mode time

-

- Standby mode is entered at SoC level.

- Standby mode is exited from Link Layer IP timer interrupt.

- System side callback is called to exit the Link Layer from deep-sleep mode (Link Layer mode is now sleep mode).

- Stop mode time

-

- The system returns in IDLE state but Link Layer is not put in deep-sleep as there is not enough time before the next radio event.

- As Link Layer is not in deep-sleep, Stop mode is entered.

2.3. Application Idle state

The application is either in Active state when the CPU executes code or in Idle state when the CPU is stopped.

The Idle state may be split into three parts:

- Pre Idle: It holds the last code to be executed before stopping the CPU.

- For a bare metal model, it runs outside a critical section so that it could be possible to implement here some code with long execution time without impacting any interrupt latency.

- For the OS model, it runs inside the critical section. The code implemented there shall be short except in the case standby mode is allowed.

- Idle: It holds the code to enter Low-power mode. A critical section is required to avoid interrupt loss due to race conditions (when WFI is used to stop the CPU). When moving out from Low-power mode, it shall be executed here the mandatory setup of the system before running any interrupt. This is required as this is the last code executed before jumping in the interrupt handler.

- Post Idle: It holds the first code to be executed when moving out from the Idle Task. It shall be executed when the Pre Idle task has been executed and only in that case.

- For the bare metal model, it runs outside a critical section so that it could be possible to implement here some code with long execution time without impacting any interrupt latency. It should be executed here any system setup that is required for the application to run but not mandatory for a coming interrupt handler.

- For the OS model, it runs inside the critical section. The code implemented there shall be short except in the case standby mode is allowed. It should be executed here any system setup that is required for the application to run.

2.4. Low-power concept summary

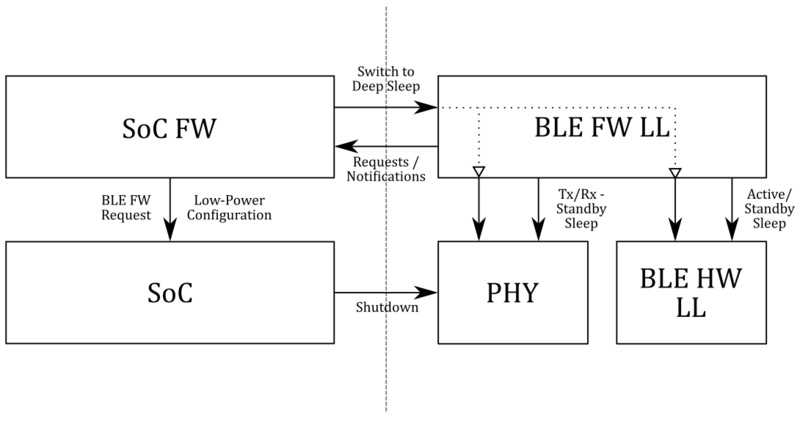

Here is a summary diagram of the STM32WBA5 low-power features.

3. Interfaces

3.1. LPM Utility

| UTIL_LPM_Init |

|---|

|

Description

|

| UTIL_LPM_DeInit |

|---|

|

Description

|

| UTIL_LPM_GetMode |

|---|

|

Description

|

| UTIL_LPM_SetStopMode |

|---|

|

Description

|

| UTIL_LPM_SetOffMode |

|---|

|

Description

|

| UTIL_LPM_EnterLowPower |

|---|

|

Description

|

3.2. Low-power platform interfaces

| PWR_EnterSleepMode |

|---|

|

Description

|

| PWR_ExitSleepMode |

|---|

|

Description

|

| PWR_EnterStopMode |

|---|

|

Description

|

| PWR_ExitStopMode |

|---|

|

Description

|

| PWR_EnterOffMode |

|---|

|

Description

|

| PWR_ExitOffMode |

|---|

|

Description

|

3.3. CPU context save & restore

| CPUcontextSave |

|---|

|

Description

|

| CPUcontextRestore |

|---|

|

Description

|

3.4. CPU peripherals save & restore

3.4.1. CPU peripheral register table

| register_backup_table |

|---|

|

Description

const volatile uint32_t* const register_backup_table[] =

{

&(SCB->CPACR), /* FPU SCB->CPACR register */

&(SysTick->CTRL), /* SysTick CTRL register */

&(SysTick->LOAD), /* SysTick LOAD register */

&(SysTick->VAL), /* SysTick VAL register */

/* USER CODE BEGIN RBL */

/* USER CODE END RBL */

};

|

3.4.2. CPU peripheral save & restore functions

| backup_system_register |

|---|

|

Description

|

| restore_system_register |

|---|

|

Description

|

4. How to

4.1. Low-power initialization & configuration

In Connectivity applications, low-power is configured in Core/Inc/app_conf.h file where the user can activate

CFG_FULL_LOW_POWERto deactivate incompatible features such as debugger and Nucleo LEDs.CFG_LPM_SUPPORTEDto activate low-power manager Utility.CFG_LPM_STDBY_SUPPORTEDto activate standby mode support.

UTIL_LPM_Init is responsible for initializing low-power manager Utility (in Core/Src/app_entry.c file). Once this is done, the user can dynamically enable or disable Stop/Standby mode with UTIL_LPM_SetStopMode/UTIL_LPM_SetOffMode APIs.

4.2. Low-power entrance when IDLE

Low-power can only be entered when application is in Idle mode.

To do so, UTIL_LPM_EnterLowPower has to be called.