1. Article purpose[edit source]

This article explains how to configure the TF-A MTD frameworks:

- SPI NOR

- SPI NAND

- SPI MEM

- FMC NAND

These frameworks represent the memory-access organisation.

They use two different configurations:

If the peripheral is assigned to another execution context, refer to How to assign an internal peripheral to a runtime context article for guidelines on peripheral assignment and configuration.

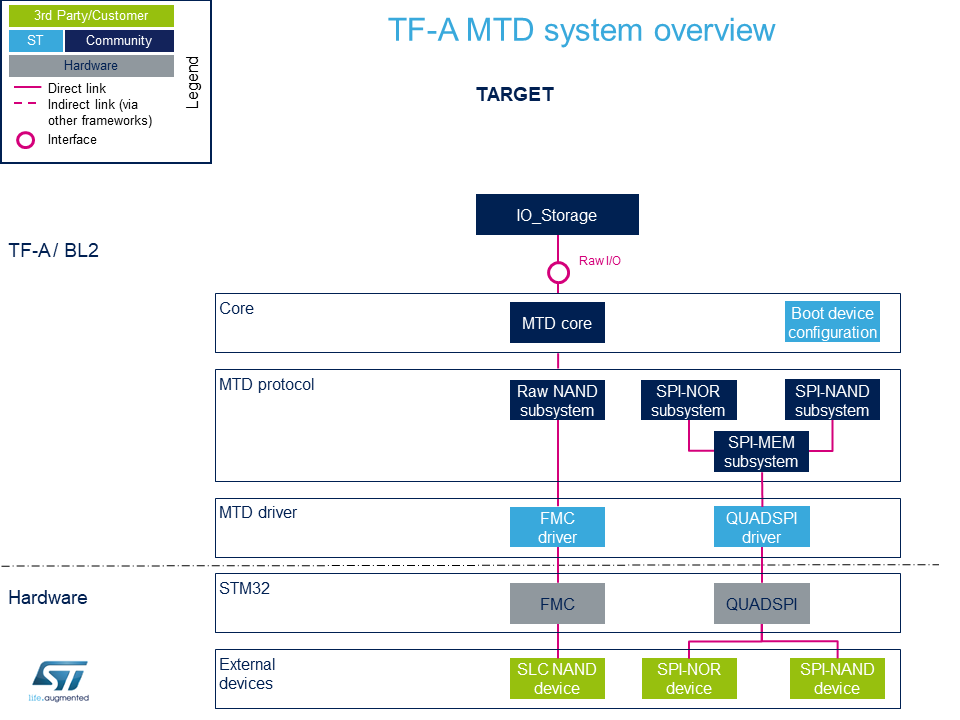

2. Framework overview[edit source]

2.1. Components description[edit source]

- IO_Storage. The IO storage provides an abstraction layer to access storage devices.

- Boot device configuration. The Boot device configuration is a platform specific add-on to manage Flash memory settings.

- MTD core. The MTD core provides an abstraction layer for raw Flash memories.

- Raw NAND subsystem. The Raw NAND protocol is used in the MTD subsystem for interfacing NAND Flash memories.

- SPI-MEM subsystem. The SPI-MEM protocol is used in the MTD subsystem for interfacing all kinds of SPI memories (NORs, NANDs).

- SPI-NAND subsystem. The SPI-NAND protocol is used in the MTD subsystem for interfacing SPI NAND Flash memories.

- SPI-NOR subsystem. The SPI-NOR protocol is used in the MTD subsystem for interfacing SPI NOR Flash memories.

- FMC driver / FMC (Hardware) . Please refer to the FMC internal peripheral.

- QUADSPI driver / QUADSPI (Hardware). Please refer to the QUADSPI internal peripheral.

3. DT configuration[edit source]

This hardware description is a combination of the STM32 microprocessor device tree files (.dtsi extension) and board device tree files (.dts extension). See the Device tree for an explanation of the device tree file split.

Pinctrl device tree configuration (and optionally to Pinctrl overview) must be added in #DT configuration (board level).

STM32CubeMX can be used to generate the board device tree. Refer to How to configure the DT using STM32CubeMX for more details.

4. Raw NAND Flash memory[edit source]

4.1. Raw NAND DT configuration[edit source]

For the DT bindings, refer to FMC_device_tree_configuration.

For the DT configuration (STM32 level), refer to FMC DT Configuration at STM32 level.

For the DT configuration (board level), refer to FMC DT Configuration at board level.

4.2. Raw NAND device configuration[edit source]

Raw NAND access uses the raw NAND framework. Some additional parameters are required by the raw NAND framework to address the memory:

- the page size

- the block size

- the number of blocks per device

- the bus width (8 or 16 bits)

- the ECC algorithm (HW BCH8/BCH4/Hamming algorithms are available). The default ECC used is ECC NONE (no error correction).

Some memories are ONFI[1] compliant. In that case, the required parameters can be directly read from the parameter description table.

For the others, the user must correctly fill-out the OTP configuration.

4.2.1. Raw NAND examples[edit source]

- ONFI raw NAND with ECC override (default from parameter table is BCH4, force to BCH8).

OTP Word 9 : 0x18000

| Use OTP | Page size | Block size | Block numbers (N * 256) | Width | ECC | ||||||||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- 8-bit raw NAND (page size: 4 Kbytes, block size: 256 Kbytes, device size: 1024 Mbytes, ECC requirement: BCH4)

OTP Word 9 : 0xA0808000

| Use OTP | Page size | Block size | Block numbers (N * 256) | Width | ECC | ||||||||||||||||||||||||||

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- 16-bit raw NAND (page size: 8 Kbytes, block size: 512 Kbytes, device size: 2048 Mbytes, ECC requirement: ON-DIE)

OTP Word 9 : 0xc0860000

| Use OTP | Page size | Block size | Block numbers (N * 256) | Width | ECC | ||||||||||||||||||||||||||

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

5. SPI NAND flash memory[edit source]

5.1. SPI NAND DT configuration[edit source]

For the DT bindings, refers to the QUADSPI_device_tree_configuration.

For the DT configuration (STM32 level), refer to QUADSPI DT Configuration at STM32 level.

For the DT configuration (board level), refer to QUADSPI DT Configuration at board level.

5.2. SPI NAND device configuration[edit source]

SPI NAND and SPI MEM frameworks are used to address such memories.

5.2.1. SPI NAND framework[edit source]

SPI NAND framework requires additional parameters:

- the page size

- the block size

- the number of blocks per device

- the number of planes per device.

These parameters must be correctly filled out by the user in OTP configuration.

By default, the READ FROM CACHE x1 command is used (opcode: 0x03). It is possible to override this command in the platform configuration to improve memory-access performance .

5.2.2. SPI NAND example[edit source]

- SPI NAND (page size: 2 Kbytes, block size: 128 Kbytes, device size: 256 Mbytes, 2 planes)

OTP Word 9 : 0x80404000

| Use OTP | Page size | Block size | Block numbers (N * 256) | Not Used | Not Used | 2 Planes | |||||||||||||||||||||||||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- Update the READ FROM CACHE x1 command to use the READ FROM CACHE x4 command (opcode: 0x6B) defined in platform file[2]

device->spi_read_cache_op.cmd.opcode = SPI_NAND_OP_READ_FROM_CACHE_4X; device->spi_read_cache_op.cmd.buswidth = SPI_MEM_BUSWIDTH_1_LINE; device->spi_read_cache_op.addr.nbytes = 2U; device->spi_read_cache_op.addr.buswidth = SPI_MEM_BUSWIDTH_1_LINE; device->spi_read_cache_op.dummy.nbytes = 1U; device->spi_read_cache_op.dummy.buswidth = SPI_MEM_BUSWIDTH_1_LINE; device->spi_read_cache_op.data.buswidth = SPI_MEM_BUSWIDTH_4_LINE; device->spi_read_cache_op.data.dir = SPI_MEM_DATA_IN;

6. SPI NOR Flash memory[edit source]

6.1. SPI NOR DT configuration[edit source]

For the DT bindings, refer to the QUADSPI_device_tree_configuration.

For the DT configuration (STM32 level), refer to QUADSPI DT Configuration at STM32 level.

For the DT configuration (board level), refer to QUADSPI DT Configuration at board level.

6.2. SPI NOR device configuration[edit source]

SPI NOR and SPI MEM frameworks are used to address such memories.

6.2.1. SPI NOR framework[edit source]

SPI NOR framework requires additional parameter:

- Device size

This parameter needs to be defined in the platform configuration file<ref_name="boot_device">.

By default, the READ command is used (opcode: 0x03). It is possible to override this command in the platform configuration to improve memory-access performance .

6.2.2. SPI NOR example[edit source]

- SPI NOR (device size: 64 Mbytes)

device->size = SZ_64M; --> Device size

- Update the READ command to use QREAD command (opcode: 0x6B) defined in platform file[2]

device->read_op.cmd.opcode = SPI_NOR_OP_READ_1_1_4; device->read_op.cmd.buswidth = SPI_MEM_BUSWIDTH_1_LINE; device->read_op.addr.nbytes = 3U; device->read_op.addr.buswidth = SPI_MEM_BUSWIDTH_1_LINE; device->read_op.dummy.nbytes = 1U; device->read_op.dummy.buswidth = SPI_MEM_BUSWIDTH_1_LINE; device->read_op.data.buswidth = SPI_MEM_BUSWIDTH_4_LINE; device->read_op.data.dir = SPI_MEM_DATA_IN;

7. How to configure the DT using STM32CubeMX[edit source]

The STM32CubeMX tool can be used to configure the STM32MPU device and get the corresponding platform configuration device tree files.

The STM32CubeMX might not support all the properties described in the above DT bindings documentation paragraph. If so, the tool inserts user sections in the generated device tree. These sections can then be edited to add some properties, and they are preserved from one generation to another. Refer to the STM32CubeMX user manual for further information.

8. References[edit source]

Please refer to the following links for additional information: