1. Article purpose[edit source]

The purpose of this article is to:

- Introduce the DSI peripheral and its main features,

- Indicate the level of security supported by this hardware block,

- Explain how each instance can be allocated to the three runtime contexts and linked to the corresponding software components,

- Explain, where necessary, how to configure the DSI peripheral.

2. Peripheral overview[edit source]

The DSI peripheral implements all the protocol functions defined in the MIPI® Display Serial Interface (MIPI® DSI) specification. It provides an interface to communicate with a DSI-compliant display. The MIPI® DSI is part of a group of communication protocols defined by the MIPI® Alliance [1].

2.1. Features[edit source]

Refer to the STM32MP15 reference manuals for the complete list of features, and to the software components, introduced below, to see which features are implemented.

2.2. Security support[edit source]

The DSI is a non-secure peripheral.

3. Peripheral usage and associated software[edit source]

Even if some MIPI DSI modes are supported by the DSI internal peripheral, in practice:

- software frameworks like U-Boot or Linux® kernel do not support all the possible modes.

- hardware integration constraints such as support for all the clock values or the pll configurations make it difficult to use all possible modes.

Select a MIPI DSI panel or bridge supporting the DSI video burst mode [2] because this mode is supported by all software frameworks and is easier to fine tune. Please consider the following recommendations when selecting a MIPI DSI panel or bridge for your project:

- Pixel data transmission

- in DSI command mode: not supported by neither U-Boot nor Linux® kernel, use instead the DSI video burst mode.

- in DSI video mode:

- burst mode: supported

- non-burst mode with sync events or pulses: supported with clock constraints to be considered [2].

- Command transmission (initialization sequence, backlight...)

3.1. Boot time[edit source]

The DSI is used at boot time for displaying a splash screen through the U-Boot framework [3].

3.2. Runtime[edit source]

3.2.1. Overview[edit source]

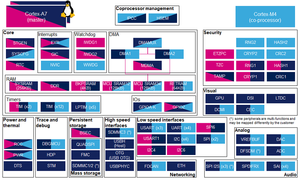

The DSI internal peripheral runs on the Arm® Cortex®-A7 non-secure core to be controlled by the Linux® DRM/KMS framework.

Chapter Peripheral assignment describes which peripheral instance can be assigned to which context.

3.2.2. Software frameworks[edit source]

| Domain | Peripheral | Software frameworks | Comment | ||

|---|---|---|---|---|---|

| Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Visual | DSI | DRM/KMS framework | |||

3.2.3. Peripheral configuration[edit source]

The configuration is applied by the firmware running in the context to which the peripheral is assigned. The configuration can be done alone via the STM32CubeMX tool for all internal peripherals, and then manually completed (particularly for external peripherals), according to the information given in the corresponding software framework article or for Linux® in the DSI device tree configuration article.

3.2.4. Peripheral assignment[edit source]

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- ☐ means that the peripheral can be assigned (☑) to the given runtime context.

- ✓ is used for system peripherals that cannot be unchecked because they are statically connected in the device.

Refer to How to assign an internal peripheral to a runtime context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Visual | DSI | DSI | ☐ | |||

4. How to go further[edit source]

Refer to the STM32 DSI application note (AN4860) [2] for a detailed description of the DSI peripheral and applicable use-cases.

Even if this application note is related to STM32 microcontrollers, it also applies to STM32 MPUs.

5. References[edit source]