1. Article purpose[edit source]

The purpose of this article is to:

- briefly introduce the DDRMCE peripheral and its main features

- indicate the level of security supported by this hardware block

- explain how to configure the DDRMCE peripheral.

2. Peripheral overview[edit source]

The DDRMCE (DDR Memory Cipher Engine) peripheral allows to defined one AES encrypted region in DDR memory.

2.1. Features[edit source]

Refer to STM32MP13 reference manuals for the complete list of features, and to the software components, introduced below, to know which features are really implemented.

DDRMCE 128-bit master key is provisioned during boot processing, in order to use AES[1] block ciphering feature. It must be fully saved in Backup RAM for low power sequences.

2.2. Security support[edit source]

DDRMCE is a securable peripheral (under ETZPC control).

3. Peripheral usage and associated software[edit source]

3.1. Boot time[edit source]

The DDRMCE, part of the DDR subsystem, is configured inside TF-A BL2 to setup the security of a DDR region. This should be done before accessing DDR region if encryption is required.

3.2. Runtime[edit source]

3.2.1. Overview[edit source]

All system bus traffic going through an encrypted region is managed on-the-fly by the DDRMCE, automatically decrypting reads and encrypting writes.

3.2.2. Software frameworks[edit source]

| Domain | Peripheral | Software components | Comment | |

|---|---|---|---|---|

| OP-TEE | Linux | |||

| RAM/Security | DDRMCE | Memory mapping | ||

3.2.3. Peripheral configuration[edit source]

The DDRMCE configuration is generated via STM32CubeMX tool, according to the region characteristics (address, length, type). This configuration is applied during boot time by the FSBL (see Boot chain overview): TF-A.

3.2.4. Peripheral assignment[edit source]

Click on the right to expand the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

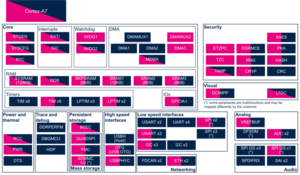

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| Security | DDRMCE | DDRMCE | ✓ | ✓ | |

4. References[edit source]