This message will disappear after all relevant tasks have been resolved.

Semantic MediaWiki

There are 1 incomplete or pending task to finish installation of Semantic MediaWiki. An administrator or user with sufficient rights can complete it. This should be done before adding new data to avoid inconsistencies.| Coming soon |

1. General recommendations[edit source]

At IC level, Eye Diagram is characterized with a specific reference resistor between USB_RREF and ground.

Verify first that USB_RREF resistor is correctly connected and has proper value and precision (3 kΩ 1%)

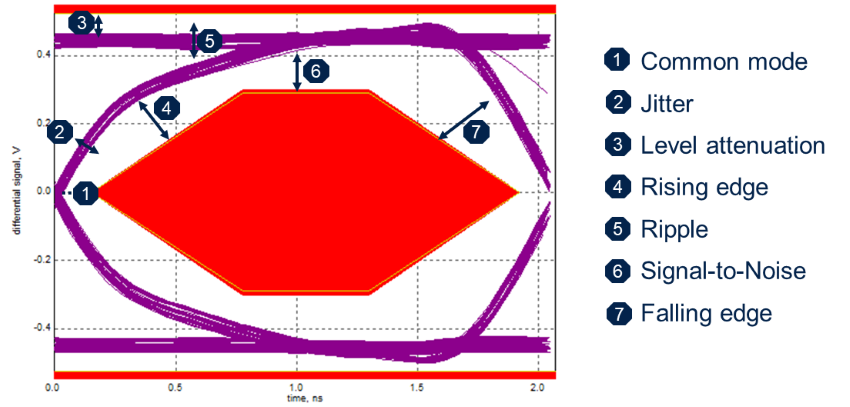

2. Eye Diagram[edit source]

2.1. Common mode troubleshooting[edit source]

- Hardware root causes to investigate

- Mismatch between D+ and D- (in terms of length and/or parallelism)

- Check layout and add common mode filter (e.g. ECMF02-2AMX6[1])

2.2. Jitter troubleshooting[edit source]

- Hardware root causes to investigate

- Too much capacitance (component or PCB) on D+/D- lines

- USB Power/GND instability

- Check decoupling / Check grounding

- Software potential tuning

Only fine tuning available. High jitter has an HW root cause in most cases.

- USBPHYC_TUNEx.HSDRVRFRED

- 0: increase rising edge but add jitter

- USBPHYC_TUNEx.INCURREN/.INCURRINT

- Reduce current increase with .INCURREN=0 or .INCURRINT=0

- USBPHYC_TUNEx.HSDRVCHKITRM

- Reduce the increase of the main level

2.3. Level attenuation or Signal-to-Noise troubleshooting[edit source]

- Hardware root causes to investigate

- too much serial resistance and capacitance (component or PCB) on D+/D- lines

- USB Power/GND instability

- Check decoupling / Check grounding

- Software potential tuning

- USBPHYC_TUNEx.HSDRVCHKITRM

- Higher the value, higher will be the level of signal.

- But noise and ripple can appear

- USBPHYC_TUNEx.HSDRVCURINCR/.HSDRVDCLEV

- Higher the value, higher will be the margin for the level.

- But jitter in the rising edge and noise can appear

2.4. Rising edge or Falling edge troubleshooting[edit source]

- Hardware root causes to investigate

- too much serial resistance and capacitance (component or PCB) on D+/D- lines

- Impedance mismatch : check characteristic impedance of lines, stubs…

- Software potential tuning

- USBPHYC_TUNEx.HSDRVRFRED

- 0 improve rising edge

- 1 slow-down rising edge.

- Potential impact on jitter

- USBPHYC_TUNEx.HSDRVCHKITRM

- Depending on level, slope is increased/decreased

- USBPHYC_TUNEx.HSDRVSLEW

- 0 normal rising edge

- 1 reduce rising edge.

- Useful to reduce a hill shape ripple on top of rising/falling edge

- USBPHYC_TUNEx.HSDRVCURINCR/.HSDRVDCLEV

- Improve slope speed.

- But jitter in the rising edge and noise can appear

2.5. Ripple troubleshooting[edit source]

- Hardware root causes to investigate

- Impedance mismatch : check characteristic impedance of lines, stubs…

- Software potential tuning

- USBPHYC_TUNEx.HSDRVCHKZTRM[1:0]

- 00: Usually open the eye but can create some jitter and ripple

- 11: Close the eye but can reduce jitter and ripple

- USBPHYC_TUNEx.HSDRVSLEW

- 0 normal rising edge

- 1 reduce rising edge.

- Useful to reduce a hill shape ripple on top of rising/falling edge

- References: