This article lists all internal peripherals embedded in STM32MP15 device and shows the assignment possibilities to the runtime contexts for each one of them.

Via this article, you can also access to individual peripheral articles in which information related to the overview and configuration can be found.

1. Internal peripherals overview[edit source]

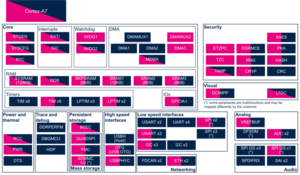

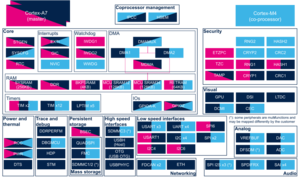

The figure below shows all peripherals embedded in STM32MP15 device, grouped per functional domains that are reused in many places of this wiki to structure the articles.

Several runtime contexts exist on STM32MP15 device[1], corresponding to the different Arm cores and associated security modes:

- Arm dual core Cortex-A7 secure (Trustzone), running a Secure Monitor or Secure OS like OP-TEE

- Arm dual core Cortex-A7 non secure , running Linux

- Arm Cortex-M4 (non-secure), running STM32Cube

Some peripherals can be strictly assigned to one runtime context: this is the case for most of the peripherals, like USART or I2C.

Other ones can be shared between several runtime contexts: this is the case for system peripherals, like PWR or RCC.

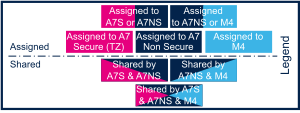

The legend below shows how assigned and shared peripherals are identified in the assignment diagram that follows:

Both the diagram below and the following summary table (in Internal peripherals assignment chapter below) are clickable in order to jump to each peripheral overview articles and get more detailed information (like software frameworks used to control them). They list STMicroelectronics recommendations. The STM32MP15 reference manual [2] may expose more possibilities than what is shown here.

2. Internal peripherals assignment[edit source]

Internal peripherals assignment table template

| rowspan="1" | Analog | rowspan="1" | ADC | ADC | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Analog | rowspan="1" | DAC | DAC | | ☐ | ☐ | Assignment (single choice) |-

STM32MP15 DFSDM internal peripheral

| rowspan="1" | Analog | rowspan="1" | VREFBUF | VREFBUF | | ☐ | | Assignment (single choice) |-

| rowspan="4" | Audio | rowspan="4" | SAI | SAI1 | | ☐ | ☐ | Assignment (single choice) |- | SAI2 | | ☐ | ☐ | Assignment (single choice) |- | SAI3 | | ☐ | ☐ | Assignment (single choice) |- | SAI4 | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Audio | rowspan="1" | SPDIFRX | SPDIFRX | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Coprocessor | rowspan="1" | IPCC | IPCC | | ☑ | ☑ | Shared (none or both) |-

| rowspan="1" | Coprocessor | rowspan="1" | HSEM | HSEM | ✓ | ✓ | ✓ | |-

| rowspan="1" | Core | rowspan="1" | RTC | RTC | ✓ | ✓ | | RTC is mandatory to resynchronize STGEN after exiting low-power modes. |-

3. Article purpose[edit source]

The purpose of this article is to:

- briefly introduce the STGEN peripheral and its main features

- indicate the level of security supported by this hardware block

- explain how it can be allocated to the runtime contexts and linked to the corresponding software components

- explain, when necessary, how to configure the STGEN peripheral.

4. Peripheral overview[edit source]

The STGEN peripheral provides the reference clock used by the Arm® Cortex®-A7 generic timer for its counters, including the system tick generation.

It is clocked by ACLK (the AXI bus clock), so caution is needed when this clock is changed; otherwise the operating system (running on the Cortex-A7) might run with a varying reference clock.

4.1. Features[edit source]

Refer to the STM32MP13 reference manuals or STM32MP15 reference manuals for the complete list of features, and to the software components, introduced below, to see which features are implemented.

4.2. Security support[edit source]

The STGEN is a single-instance peripheral that can be accessed via the two following register sets:

- STGENC for the control. That is, a secure port (under ETZPC control).

- STGENR for the read-only access. That is, a non secure port.

5. Peripheral usage and associated software[edit source]

5.1. Boot time[edit source]

The STGEN is first initialized by the ROM code, then updated by the FSBL (see Boot chain overview) once the clock tree is set up.

5.2. Runtime[edit source]

5.2.1. Overview[edit source]

Linux® and OP-TEE use the Arm Cortex-A7 generic timer that gets its counter from the STGEN, but this is transparent at run time.

Hence there is no runtime allocation decision for this peripheral: both contexts are selected by default.

5.2.2. Software frameworks[edit source]

5.2.2.1. On STM32MP13x lines  [edit source]

[edit source]

| Domain | Peripheral | Software components | Comment | |

|---|---|---|---|---|

| OP-TEE | Linux | |||

| Core | STGEN | see comment | see comment | Not applicable as the STGEN peripheral is configured at boot time and not accessed at runtime |

5.2.2.2. On STM32MP15x lines  [edit source]

[edit source]

| Domain | Peripheral | Software components | Comment | ||

|---|---|---|---|---|---|

| OP-TEE | Linux | STM32Cube | |||

| Core | STGEN | see comment | see comment | Not applicable as the STGEN peripheral is configured at boot time and not accessed at runtime | |

5.2.3. Peripheral configuration[edit source]

5.2.4. Peripheral assignment[edit source]

5.2.4.1. On STM32MP13x lines  [edit source]

[edit source]

Click on the right to expand the legend...

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- ☐ means that the peripheral can be assigned (☑) to the given runtime context.

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in STM32 MPU Embedded Software distribution.

- ✓ is used for system peripherals that cannot be unchecked because they are statically connected in the device.

Refer to How to assign an internal peripheral to a runtime context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP13 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| Core | STGEN | STGEN | ✓ | ✓ | |

5.2.4.2. On STM32MP15x lines  [edit source]

[edit source]

Click on the right to expand the legend...

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- ☐ means that the peripheral can be assigned (☑) to the given runtime context.

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in STM32 MPU Embedded Software distribution.

- ✓ is used for system peripherals that cannot be unchecked because they are statically connected in the device.

Refer to How to assign an internal peripheral to a runtime context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core | STGEN | STGEN | ✓ | ✓ | ||

6. References[edit source]

| rowspan="1" | Core | rowspan="1" | SYSCFG | SYSCFG | | ✓ | ✓ | |-

| rowspan="2" | Core/DMA | rowspan="2" | DMA | DMA1 | | ☐ | ☐ | Assignment (single choice) |- | DMA2 | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Core/DMA | rowspan="1" | DMAMUX | DMAMUX | | ☐ | ☐ | Shareable (multiple choices supported) |-

| rowspan="1" | Core/DMA | rowspan="1" | MDMA | MDMA | ☐ | ☐ | | Shareable (multiple choices supported) |-

| rowspan="1" | Core/Interrupts | rowspan="1" | EXTI | EXTI | | ✓ | ✓ | Shared |-

| rowspan="1" | Core/Interrupts | rowspan="1" | GIC | GIC | ✓ | ✓ | | |-

| rowspan="1" | Core/Interrupts | rowspan="1" | NVIC | NVIC | | | ✓ | |-

| rowspan="2" | Core/IOs | rowspan="2" | GPIO | GPIOA-K | | ☐ | ☐ | Shareable (with pin granularity) |- | GPIOZ | ☐ | ☐ | ☐ | Shareable (with pin granularity) |-

| rowspan="1" | Core/RAM | rowspan="1" | BKPSRAM | BKPSRAM | ☐ | ☐ | | Assignment (single choice) |-

| rowspan="1" | Core/RAM | rowspan="1" | DDR via DDRCTRL | DDR | ✓ | ✓ | | |-

| rowspan="1" | Core/RAM | rowspan="1" | RETRAM | RETRAM | ☐ | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Core/RAM | rowspan="1" | SYSRAM | SYSRAM | ☐ | ☐ | | Shareable (multiple choices supported) |-

| rowspan="5" | Core/Timers | rowspan="5" | LPTIM | LPTIM1 | | ☐ | ☐ | Assignment (single choice) |- | LPTIM2 | | ☐ | ☐ | Assignment (single choice) |- | LPTIM3 | | ☐ | ☐ | Assignment (single choice) |- | LPTIM4 | | ☐ | ☐ | Assignment (single choice) |- | LPTIM5 | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="14" | Core/Timers | rowspan="14" | TIM | TIM1 (APB2 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM2 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM3 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM4 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM5 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM6 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM7 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM8 (APB2 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM12 (APB1 group) | ☐ | ☐ | ☐ | Assignment (single choice)

TIM12 or TIM15 can be used for HSI/CSI calibration[1] |- | TIM13 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM14 (APB1 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM15 (APB2 group) | ☐ | ☐ | ☐ | Assignment (single choice)

TIM12 or TIM15 can be used for HSI/CSI calibration[1] |- | TIM16 (APB2 group) | | ☐ | ☐ | Assignment (single choice) |- | TIM17 (APB2 group) | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="2" | Core/Watchdog | rowspan="2" | IWDG | IWDG1 | ☐ | | | |- | IWDG2 | ☐ | ☐ | | Shared (none or both):

- Cortex-A7 non secure for reload

- Cortex-A7 secure for early interrupt handling

|-

| rowspan="1" | Core/Watchdog | rowspan="1" | WWDG | WWDG | | | ☐ | |-

| rowspan="1" | High speed interface | rowspan="1" | OTG (USB OTG) | OTG (USB OTG) | | ☐ | | |-

| rowspan="1" | High speed interface | rowspan="1" | USBH (USB Host) | USBH (USB Host) | | ☐ | | |-

| rowspan="1" | High speed interface | rowspan="1" | USBPHYC (USB HS PHY controller) | USBPHYC (USB HS PHY controller) | | ☐ | | |-

| rowspan="6" | Low speed interface | rowspan="6" | I2C | I2C1 | | ☐ | ☐ | Assignment (single choice) |- | I2C2 | | ☐ | ☐ | Assignment (single choice) |- | I2C3 | | ☐ | ☐ | Assignment (single choice) |- | I2C4 | ☐ | ☐ | | Assignment (single choice).

Used for PMIC control on ST boards. |- | I2C5 | | ☐ | ☐ | Assignment (single choice) |- | I2C6 | ☐ | ☐ | | Assignment (single choice) |-

| rowspan="6" | Low speed interface

or

audio | rowspan="6" | SPI | SPI2S1 | | ☐ | ☐ | Assignment (single choice) |- | SPI2S2 | | ☐ | ☐ | Assignment (single choice) |- | SPI2S3 | | ☐ | ☐ | Assignment (single choice) |- | SPI4 | | ☐ | ☐ | Assignment (single choice) |- | SPI5 | | ☐ | ☐ | Assignment (single choice) |- | SPI6 | ⬚ | ☐ | | Assignment (single choice) |-

| rowspan="8" | Low speed interface | rowspan="8" | USART | USART1 | ☐ | ☐ | | Assignment (single choice) |- | USART2 | | ☐ | ☐ | Assignment (single choice) |- | USART3 | | ☐ | ☐ | Assignment (single choice) |- | UART4 | | ☐ | ☐ | Assignment (single choice).

Used for Linux® serial console on ST boards. |- | UART5 | | ☐ | ☐ | Assignment (single choice) |- | USART6 | | ☐ | ☐ | Assignment (single choice) |- | UART7 | | ☐ | ☐ | Assignment (single choice) |- | UART8 | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Mass storage | rowspan="1" | FMC | FMC | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Mass storage | rowspan="1" | QUADSPI | QUADSPI | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="3" | Mass storage | rowspan="3" | SDMMC | SDMMC1 | | ☐ | | |- | SDMMC2 | | ☐ | | |- | SDMMC3 | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Networking | rowspan="1" | ETH | ETH | | ☐ | | Assignment (single choice) |-

| rowspan="2" | Networking | rowspan="2" | FDCAN | FDCAN1 | | ☐ | ☐ | Assignment (single choice) |- | FDCAN2 | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Power & Thermal | rowspan="1" | DTS | DTS | | ☐ | | |-

| rowspan="1" | Power & Thermal | rowspan="1" | PWR | PWR | ✓ | ✓ | ✓ | |-

| rowspan="1" | Power & Thermal | rowspan="1" | RCC | RCC | ✓ | ✓ | ✓ | |-

| rowspan="1" | Security | rowspan="1" | BSEC | BSEC | ✓ | ✓ | | |-

| rowspan="2" | Security | rowspan="2" | CRC | CRC1 | | ☐ | | |- | CRC2 | | | ☐ | |-

STM32MP15 CRYP internal peripheral

| rowspan="1" | Security | rowspan="1" | ETZPC | ETZPC | ✓ | ✓ | ✓ | |-

| rowspan="2" | Security | rowspan="2" | HASH | HASH1 | ☐ | ☐ | | Assignment (single choice) |- | HASH2 | | | ☐ | |-

| rowspan="2" | Security | rowspan="2" | RNG | RNG1 | ☐ | ☐ | | Assignment (single choice) |- | RNG2 | | | ☐ | |-

| rowspan="1" | Security | rowspan="1" | TZC | TZC | ✓ | | | |-

| rowspan="1" | Security | rowspan="1" | TAMP | TAMP | ✓ | ✓ | | |-

| rowspan="1" | Trace & Debug | rowspan="1" | DBGMCU | DBGMCU | | | | No assignment |-

| rowspan="1" | Trace & Debug | rowspan="1" | HDP | HDP | | ☐ | | |-

| rowspan="2" | Trace & Debug | rowspan="2" | ETM | ETM0 | ✓ | ✓ | | |- | ETM1 | ✓ | ✓ | | |-

| rowspan="1" | Trace & Debug | rowspan="1" | STM | STM | | | | No assignment possible |-

| rowspan="1" | Visual | rowspan="1" | CEC | CEC | | ☐ | ☐ | Assignment (single choice) |-

| rowspan="1" | Visual | rowspan="1" | DCMI | DCMI | |☐ |☐ | Assignment (single choice) |-

| rowspan="1" | Visual | rowspan="1" | DSI | DSI | | ☐ | | |-

| rowspan="1" | Visual | rowspan="1" | GPU | GPU | | ☐ | | |-

| rowspan="1" | Visual | rowspan="1" | LTDC | LTDC | | ☐ | | |-

|}

7. References[edit source]