1. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the TIM peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

The TIM peripheral is a multi-channel timer unit, available in various configurations, depending on the instance used. There are basically following categories: advanced-control timers, general-purpose timers and basic timers.

The TIM can provide: PWM with complementary output and dead-time insertion, break detection, input capture[1], quadrature encoder[2] interface (typically used for rotary encoders), trigger source for other internal peripherals like: ADC[3], DFSDM[4]. The full list can be found in Peripherals Interconnect matrix in the reference manual.

The TIM peripheral is available in different configurations, depending on the selected instance :

- TIM1 and TIM8 are advanced-control timers, with 6 independent channels.

- TIM2, TIM3, TIM4 and TIM5 are general-purpose timers, with 4 independent channels.

- TIM12, TIM13 and TIM14 are general-purpose timers, with 2 (TIM12) or 1 (TIM13 and TIM14) independent channels.

- TIM15, TIM16 and TIM17 are also general-purpose timers, with 2 (TIM15) or 1 (TIM16 and TIM17) independent channels. Compare to TIM12, TIM13 and TIM14, this configuration brings some features that are very useful for motor control (like break function, DMA burst mode control, complementary output with dead-time insertion, ...)

- TIM6 and TIM7 are basic timers

On STM32MP25x lines ![]() , additional instances are available:

, additional instances are available:

- TIM20 is an advanced-control timer, with 6 independent channels.

- TIM10 and TIM11 are general-purpose timers with 1 channel.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

3.1. Boot time assignment[edit | edit source]

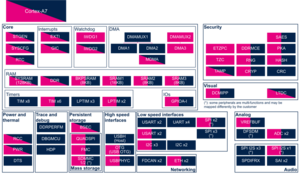

3.1.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 non-secure (U-Boot) | |||

| Core/Timers | TIM | TIMx (x = 1 to 8, APB2 group) |

⬚ | |||

| TIMx (x = 2 to 7, APB1 group) |

⬚ | |||||

| TIMx (x = 12 to 17, APB6 group) |

⬚ | ⬚ | ||||

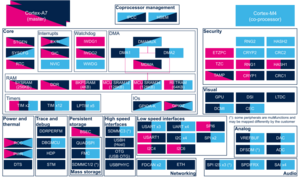

3.1.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 non-secure (U-Boot) | |||

| Core/Timers | TIM | TIMx (x = 2 to 7, 12, 13, 14. APB1 group) | ⬚ | |||

| TIMx (x = 1, 8, 15, 16, 17. APB2 group) | ⬚ | |||||

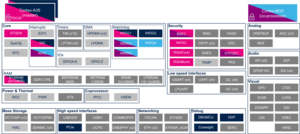

3.1.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 non-secure (U-Boot) | |||

| Core/Timers | TIM | TIMx (x = 1 to 8, 10 to 17, 20) | ⬚ | ⬚ | ||

3.2. Runtime assignment[edit | edit source]

3.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

TIM12 and/or TIM15 can be allocated to the Arm® Cortex®-A7 secure core to be controlled in the secure monitor (OP-TEE).

TIM13, TIM14, TIM16 and TIM17 can also be allocated to the Arm® Cortex®-A7 secure context, but it is not supported yet by OpenSTLinux.

| RCC[5] owns one prescaler per TIM group corresponding to APB1, APB2 and APB6 buses: TIMG1PRE, TIMG2PRE and TIMG3PRE, respectively. TIMG3PRE is securable in RCC. The allocation to Cortex-A7 contexts should ideally be done on a per group basis to get independent clocking setup on each side, this is why the TIM instances groups are shown in the summary table below. |

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| Core/Timers | TIM | TIM1 (APB2 group) | ☐ | ||

| TIM2 (APB1 group) | ☐ | ||||

| TIM3 (APB1 group) | ☐ | ||||

| TIM4 (APB1 group) | ☐ | ||||

| TIM5 (APB1 group) | ☐ | ||||

| TIM6 (APB1 group) | ☐ | ||||

| TIM7 (APB1 group) | ☐ | ||||

| TIM8 (APB2 group) | ☐ | ||||

| TIM12 (APB6 group) | ☐ | ☐ | Assignment (single choice) TIM12 or TIM15 can be used for HSI/CSI calibration[6] | ||

| TIM13 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

| TIM14 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

| TIM15 (APB6 group) | ☐ | ☐ | Assignment (single choice) TIM12 or TIM15 can be used for HSI/CSI calibration[6] | ||

| TIM16 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

| TIM17 (APB6 group) | ☐ | ☐ | Assignment (single choice) | ||

3.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

TIM12 and/or TIM15 can be allocated to the Arm® Cortex®-A7 secure core to be controlled in the secure monitor (TF-A or OP-TEE).

| RCC[5] owns one prescaler per TIM group corresponding to APB1 and APB2 buses: TIMG1PRE and TIMG2PRE, respectively. The allocation to Cortex-A7 or the Cortex-M4 should ideally be done on a per group basis to get independent clocking setup on each side, this is why the TIM instances groups are shown in the summary table below. |

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core/Timers | TIM | TIM1 (APB2 group) | ☐ | ☐ | Assignment (single choice) | |

| TIM2 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM3 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM4 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM5 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM6 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM7 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM8 (APB2 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM12 (APB1 group) | ☐ | ☐ | ☐ | Assignment (single choice) TIM12 or TIM15 can be used for HSI/CSI calibration[6] | ||

| TIM13 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM14 (APB1 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM15 (APB2 group) | ☐ | ☐ | ☐ | Assignment (single choice) TIM12 or TIM15 can be used for HSI/CSI calibration[6] | ||

| TIM16 (APB2 group) | ☐ | ☐ | Assignment (single choice) | |||

| TIM17 (APB2 group) | ☐ | ☐ | Assignment (single choice) | |||

3.2.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 non-secure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 non-secure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Core/Timers | TIM | TIM1 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||

| TIM10 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM11 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM12 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM13 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM14 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM15 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM16 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM17 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM2 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM20 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM3 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM4 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM5 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM6 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM7 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

| TIM8 | ⬚OP-TEE | ☐ | ⬚ | ☐ | ||||

4. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the TIM peripheral for the embedded software components listed in the above tables.

- Linux®: PWM, the IIO, and the Counter frameworks

- OP-TEE: OP-TEE TIM driver , to perform HSI and CSI calibrations[6] in RCC

- STM32Cube: HAL TIM driver

5. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

For Linux kernel configuration, please refer to TIM device tree configuration and TIM Linux driver articles.

6. How to go further[edit | edit source]

STM32 cross-series timer overview[7] application note.

7. References[edit | edit source]