1. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the IWDG peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

The IWDG peripheral is a watchdog unit that can be used to protect application frameworks running on Cortex-A7 from endless loops. This peripheral supports an independent clocking source in order to be able to continue running even when the rest of the system is in low power mode (STOP, STANDBY). Another important feature of this block is the early interrupt feature that allows to trigger an interrupt at a given power supply threshold before reaching the final reset: this gives the opportunity to run a recovery mechanism that will try to revive the system with minimum impact.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

3.1. Boot time assignment[edit | edit source]

Pay attention to the fact that IWDG can be configured to be automatically active at startup (without any software intervention) via BSEC. When this is the case, the watchdog is anyway frozen during ROM code execution but it will start to decrement its counter as soon as the ROM code is left so it is important to reload the watchdog from the boot chain in this case. This behavior is implemented for IWDG2 only in STMicroelectronics distribution.

Notice also that BSEC features some freeze bits that allow to freeze IWDG during platform Stop and Standby low power periods, avoiding to have to wake up (via RTC) for the only purpose of reloading the watchdog.

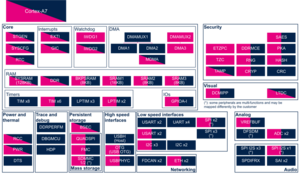

3.1.1. On STM32MP1 series[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 non-secure (U-Boot) | |||

| Core/Watchdog | IWDG | Any instance | ✓ | ☐ | ☐ | |

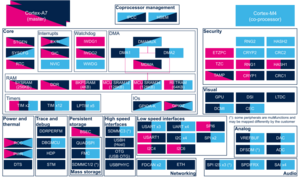

3.1.2. On STM32MP2 series[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 non-secure (U-Boot) | |||

| Core/Watchdog | IWDG | IWDG1 | ✓ | ☑ | ☐ | |

| IWDG2 | ✓ | ☐ | ☐ | |||

| IWDG3 | ||||||

| IWDG4 | ||||||

| IWDG5 | ||||||

3.2. Runtime assignment[edit | edit source]

IWDG1 can be allocated to the Cortex-A secure, which can export it to non-secure through SMC.

IWDG2 can be allocated to the Cortex-A non-secure. In this configuration, the secure monitor (from OP-TEE or TF-A) is able to receive IWDG early interrupts that can be used to save some logs before reset or, on STM32MP15x lines ![]() only, in a tentative to reset the Cortex-A7 without interfering with Cortex-M4 execution.

only, in a tentative to reset the Cortex-A7 without interfering with Cortex-M4 execution.

3.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| Core/Watchdog | IWDG | IWDG1 | ☑ | ☐ | |

| IWDG2 | ☐ | ☐ | Shared (none or both):

| ||

3.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core/Watchdog | IWDG | IWDG1 | ☐ | ☐ | ||

| IWDG2 | ☐ | ☐ | Shared (none or both):

| |||

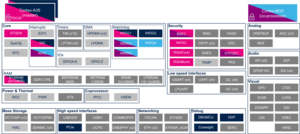

3.2.3. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 non-secure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 non-secure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Core/Watchdog | IWDG | IWDG1 | ☑OP-TEE ☑TF-A BL31 |

☐ | ||||

| IWDG2 | ☐OP-TEE ☐TF-A BL31 |

☐ | ||||||

| IWDG3 | ☐ | ☐ | ||||||

| IWDG4 | ☐ | ☐ | ||||||

| IWDG5 | ☐ | |||||||

4. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the IWDG peripheral for the embedded software components listed in the above tables.

- OP-TEE: IWDG driver

- Linux®: Linux watchdog framework, ARM SMC watchdog driver and IWDG driver

- TF-A: IWDG driver

- U-Boot: ARM SMC watchdog driver

5. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.