1. Article purpose[edit source]

The purpose of this article is to

- briefly introduce the FMC peripheral and its main features

- indicate the level of security supported by this hardware block

- explain how each instance can be allocated to the three runtime contexts and linked to the corresponding software components

- explain, when needed, how to configure the FMC peripheral.

2. Peripheral overview[edit source]

The FMC peripheral includes two memory controllers:

- The NOR/PSRAM memory controller

- The NAND memory controller

2.1. NOR/PSRAM memory controller (or external bus interface controller)[edit source]

The FMC NOR/PSRAM memory controller is used to interface static memory devices, but it is also used to interface Ethernet devices, LCD devices, .... .

The FMC NOR/PSRAM controller generates the appropriate signal timings to drive the following types of memories:

- Asynchronous SRAM, FRAM and ROM

- 8 bits

- 16 bits

- PSRAM (CellularRAM™)

- Asynchronous mode

- Burst mode for synchronous accesses with configurable option to split burst access when crossing boundary page for CRAM 1.5.

- Multiplexed or non-multiplexed

- NOR Flash memory

- Asynchronous mode

- Burst mode for synchronous accesses

- Multiplexed or non-multiplexed

The FMC NOR/PSRAM controller supports a wide range of devices through programmable timings among which:

- Programmable wait states (up to 15)

- Programmable bus turnaround cycles (up to 15)

- Programmable output enable and write enable delays (up to 15)

- Independent read and write timings and protocol to support the widest variety of memories and timings

- Programmable continuous clock output.

The FMC NOR/PSRAM controller supports up to four external devices.

2.2. NAND Flash controller[edit source]

The FMC NAND Flash controller is used to interface STM32 MPU with SLC 8-bit or 16-bit NAND Flash memory devices.

The FMC NAND Flash controller supports:

- Programmable error correction capability (ECC) using BCH8 code, BCH4 code or Hamming code

- Programmable page size of 2048, 4096 and 8192 bytes

- Programmable memory timings

- Multiple dice per package.

2.3. Features[edit source]

Refer to STM32MP15 reference manuals for the complete list of features, and to the software components, introduced below, to know which features are really implemented.

2.4. Security support[edit source]

The FMC is a non-secure peripheral.

3. Peripheral usage and associated software[edit source]

3.1. Boot time[edit source]

The FMC NAND Flash controller is the boot device that supports serial boot for Flash programming with STM32CubeProgrammer.

3.2. Runtime[edit source]

3.2.1. Overview[edit source]

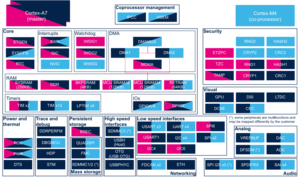

The FMC instance can be allocated to:

- the Arm® Cortex®-A7 non-secure core to be controlled in Linux® by the MTD framework

or

- the Arm® Cortex®-M4 to be controlled in STM32Cube MPU Package by FMC HAL driver

Chapter #Peripheral assignment describes which instance can be assigned to which context.

3.2.2. Software frameworks[edit source]

| Domain | Peripheral | Software components | Comment | ||

|---|---|---|---|---|---|

| OP-TEE | Linux | STM32Cube | |||

| Mass storage | FMC | Linux MTD Framework | STM32Cube FMC driver | ||

3.2.3. Peripheral configuration[edit source]

The configuration is applied by the firmware running in the context to which the peripheral is assigned. The configuration can be done alone via the STM32CubeMX tool for all internal peripherals, and then manually completed (particularly for external peripherals), according to the information given in the corresponding software framework article.

For Linux kernel configuration, please refer to FMC device tree configuration

3.2.4. Peripheral assignment[edit source]

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- ☐ means that the peripheral can be assigned (☑) to the given runtime context.

- ✓ is used for system peripherals that cannot be unchecked because they are statically connected in the device.

Refer to How to assign an internal peripheral to a runtime context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Mass storage | FMC | FMC | ☐ | ☐ | Assignment (single choice) | |

4. How to go further[edit source]

5. References[edit source]