# **RETRAM** internal memory

# **RETRAM** internal memory

Stable: 04.02.2020 - 15:59 / Revision: 04.02.2020 - 15:50

## **RETRAM internal memory**

A quality version of this page, approved on 4 February 2020, was based off this revision.

| Contents                                    |   |

|---------------------------------------------|---|

| 1 Peripheral overview4                      |   |

| 1.1 Features                                | ļ |

| 1.2 Security support4                       |   |

| 2 Peripheral usage and associated software5 |   |

| 2.1 Boot time                               |   |

| 2.2 Runtime                                 |   |

| 2.2.1 Overview 5                            | 5 |

| 2.2.2 Software frameworks                   | 5 |

| 2.2.3 Peripheral configuration5             | 5 |

| 2.2.4 Peripheral assignment                 | 5 |

# 1 Peripheral overview

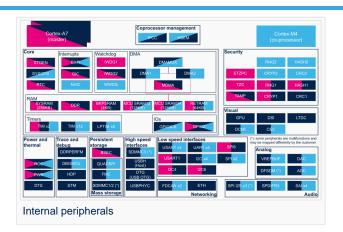

The **RETRAM** internal memory is 64 Kbytes wide and is physically near to the Arm<sup>®</sup>Cortex<sup>®</sup>-M4 for optimized performance from the core. It is located in the VSW power domain, allowing it to be supplied during Standby low power mode, and to retain retention firmware that can be executed very quickly by the Cortex-M4 on wake up from Standby mode.

### 1.1 Features

Refer to STM32MP15 reference manuals for the complete feature list, and to the software components introduced below to see which features are actually implemented.

## 1.2 Security support

The RETRAM is a **secure** peripheral (under ETZPC control).

# 2 Peripheral usage and associated software

#### 2.1 Boot time

Linux<sup>®</sup> remoteproc framework (running on the Cortex-A7) loads the Cortex-M4 firmware to the RETRAM, starting at address 0x00000000. At least, it must load the part of the firmware containing the vector table, since the Cortex-M4 reset entry point is address 0x00000004. The rest of the firmware code is loaded into the MCU SRAM. The overall memory mapping is shown in the platform memory mapping section.

#### 2.2 Runtime

#### 2.2.1 Overview

The Cortex-M4 vector table is mapped from address 0x000000000 (so to the RETRAM) at reset, but it can be remapped by software to any other location by means of the vector table offset register (VTOR). Beyond the reset entry point (0x00000004), the exception table also contains the software entries table used by the NVIC to branch the software execution to the right interrupt service routine.

While going to Standby low power mode, the RETRAM can remain supplied, so it can preserve a (small) Cortex-M4 piece of retention firmware that is executed on wake up when the ROM code (running on Cortex-A7) restarts the Cortex-M4. All these constraints make the RETRAM the minimum (and default) choice for Cortex-M4 firmware.

#### RETRAM can be allocated to:

the Cortex-A7 secure to be used under OP-TEE.

or

the Cortex-A7 non-secure to be used under Linux as reserved memory.

or

• the Cortex-M4 for use with the STM32Cube MPU Package, either for **runtime firmware** that ca be mapped in both RETRAM and MCU SRAM, or for **retention firmware** that only fits into the RETRAM, but could have some data in MCU SRAM (keeping in mind that these data are lost while entering Standby low power mode).

#### 2.2.2 Software frameworks

| Domain   | Peripheral | So                 | Comment               |               |  |

|----------|------------|--------------------|-----------------------|---------------|--|

| OP-TEE   | Linux      | STM32Cube          |                       |               |  |

| Core/RAM | RETRAM     | OP-TEE<br>overview | Linux reserved memory | STM32Cub<br>e |  |

#### 2.2.3 Peripheral configuration

The configuration is applied by the firmware running in the context to which the peripheral is assigned. The configuration can be done alone via the STM32CubeMX tool for all internal peripherals, and then manually completed (especially for external peripherals), according to the information given in the corresponding software framework article.

### 2.2.4 Peripheral assignment

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- means that the peripheral can be assigned () to the given runtime context.

- is used for system peripherals that cannot be unchecked because they are statically connected in the device.

Refer to How to assign an internal peripheral to a runtime context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals

| Domain   | Periphera          |                       | Runtime         | allocation | Comment                    |

|----------|--------------------|-----------------------|-----------------|------------|----------------------------|

|          | Cortex-A7          | Cortex-A7             | Cortex-M4       |            |                            |

| Instance | secure<br>(OP-TEE) | non-secure<br>(Linux) | (STM32Cub<br>e) |            |                            |

| Core/RAM | RETRAM             | RETRAM                |                 |            | Assignment (single choice) |

Arm® is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

Cortex®

Linux<sup>®</sup> is a registered trademark of Linus Torvalds.

Microprocessor Unit

Open Portable Trusted Execution Environment

Random Access Memory (Early computer memories generally hadserial access. Memories where any given address can be accessed when desired were then called "random access" to distinguish them from the memories where contents can only be accessed in a fixed order. The term is used today for volatile random-acces ssemiconductor memories.)